# Narrowband CMOS RF Low-Noise Amplifiers

Prof. Thomas H. Lee Stanford University tomlee@ee.stanford.edu http://www-smirc.stanford.edu

T. Lee, Paul G. Allen Center for Integrated Systems

# Outline

- □ A brief review of classic two-port noise optimization

- **Conditions for minimum noise figure**

- □ The fundamental importance of correlations

- □ MOSFET noise models in the short-channel regime

- **Equivalent two-port noise generators**

- □ Second-order noise sources

- Power constrained noise optimization

- Experimental results on devices and circuits

- □ Summary and conclusions

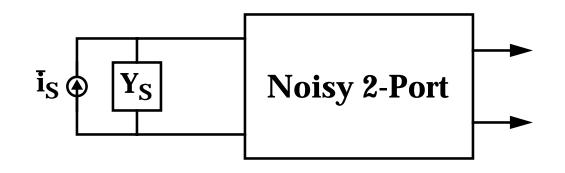

**Consider noise in an arbitrary (but linear) system:**

- Thermal noise of source represented by i<sub>S</sub>

- □ Source admittance is Y<sub>S</sub>

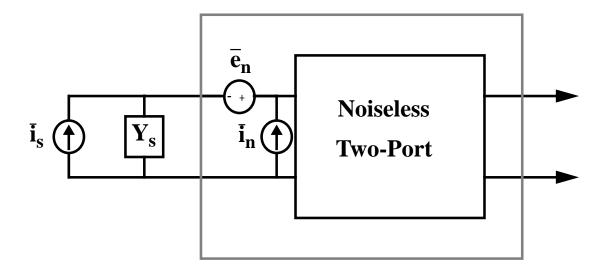

□ The noisy two-port may be modeled as follows:

- □ In general, the external noise sources will be partially *correlated*

- Correlations arise because an internal noise source may contribute to both i<sub>n</sub> and e<sub>n</sub> in general

- **Correlations have strong implications for noise performance**

- Noise factor, F, is defined as the ratio of the total output noise power divided by that part of the output noise power due to the input source, when source is at 290K

- □ Therefore:

$$F = \frac{\overline{i_s^2} + \overline{|i_n + Y_s e_n|^2}}{\frac{i_s^2}{s}}$$

**Let noise current**  $i_n$  be expressed as sum of two terms

□ First term, i<sub>u</sub>, is fully uncorrelated with noise voltage e<sub>n</sub>.

Other term, i<sub>c</sub>, is fully correlated with e<sub>n</sub>.

Since i<sub>c</sub> is correlated with e<sub>n</sub>, we may write one as proportional to the other:

$$i_c = Y_c e_n$$

- □ Note that Y<sub>c</sub> has the dimensions of an admittance

- Correlation admittance is a mathematical construct, and is not what one measures with an impedance meter

- **Re-write F as**

$$F = 1 + \frac{\overline{\left|\frac{i_{n} + Y_{S}e_{n}\right|^{2}}{\overline{i_{S}^{2}}}}}{\overline{i_{S}^{2}}} = 1 + \frac{\overline{\frac{i_{n}^{2} + |Y_{c} + Y_{S}|^{2}e_{n}^{2}}{\overline{i_{S}^{2}}}}{\overline{i_{S}^{2}}}$$

T. Lee, Paul G. Allen Center for Integrated Systems

□ Next, define effective noise resistances (conductances):

$$R_n \equiv \frac{\overline{e_n^2}}{4kT\Delta f}, G_u \equiv \frac{\overline{i_u^2}}{4kT\Delta f}, G_S \equiv \frac{\overline{i_S^2}}{4kT\Delta f}$$

□ Also:

$$\Box \quad \mathbf{Y}_{\mathbf{c}} = \mathbf{G}_{\mathbf{c}} + \mathbf{j}\mathbf{B}_{\mathbf{c}}$$

$$\Box \quad \mathbf{Y}_{\mathbf{S}} = \mathbf{G}_{\mathbf{S}} + \mathbf{j}\mathbf{B}_{\mathbf{S}}$$

#### □ Finally obtain:

$$F = 1 + \frac{G_u}{G_s} + \frac{R_n}{G_s} \left[ \left( G_s + G_c \right)^2 + \left( B_s + B_c \right)^2 \right]$$

T. Lee, Paul G. Allen Center for Integrated Systems

□ Minimum F occurs when  $B_s = -B_c = B_{opt}$  and

$$G_s = \sqrt{\frac{G_u}{R_n} + G_c^2} = G_{opt}$$

□ Minimum F is

$$F_{min} = 1 + 2R_n \left[ \sqrt{\frac{G_u}{R_n} + G_c^2} + G_c^2 \right]$$

□ In general,

$$F = F_{min} + \frac{R_n}{G_s} \left[ \left( G_s - G_{opt} \right)^2 + \left( B_s - B_{opt} \right)^2 \right]$$

□ Thus, contours of constant noise figure are circles centered about (G<sub>opt</sub>, B<sub>opt</sub>) in the admittance or Smith plane

Narrowband CMOS RF Low-Noise Amplifiers

- Source admittance for optimum noise match does not generally have any relation to the conditions for optimum power gain

- **D** Possible to have great noise figure and little or no gain

- Possible to have great noise figure and a poor impedance match

- Classical noise optimization also does not consider power consumption directly

- Modified approach required to balance all parameters of practical interest

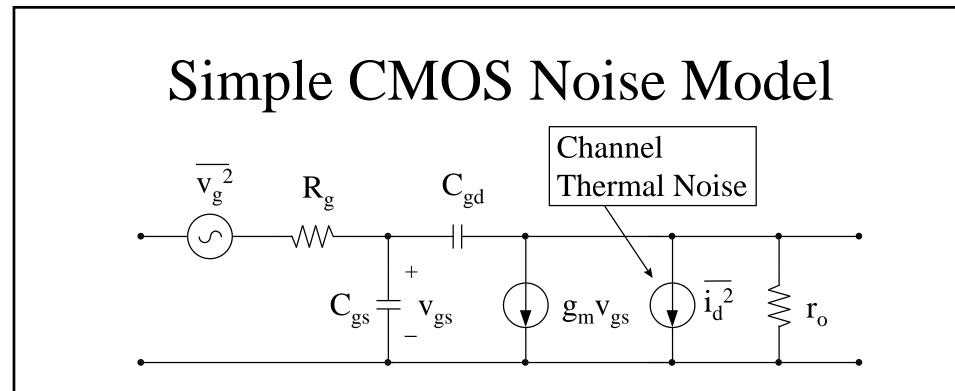

• Channel thermal noise is dominant.

$$\overline{i_d^2} = 4kTB\gamma g_{d0}$$

• Gate resistance minimized by good layout.

Stanford University

# **Channel Thermal Noise**

• Current HSPICE Implementation:

$$\overline{i_d^2} = \frac{8}{3} kTBg_m \qquad (\text{NLEV} < 3)$$

$$\overline{i_d^2} = \frac{8}{3} kTB \cdot K' \left( V_{gs} - V_T \right) \frac{1 + a + a^2}{1 + a} GDSNOI \qquad (\text{NLEV} = 3)$$

$$a = 1 - \frac{V_{ds}}{V_{dsat}}$$

• BSIM-3 Implementation:

$$\overline{i_d^2} = \frac{4kT\mu_{eff}}{L_{eff}^2} |Q_{inv}|$$

Stanford University

= 3)

LNA Input Stage

$$Z_{in} = s(L_s + L_g) + \frac{1}{sC_{gs}} + \left(\frac{g_m}{C_{gs}}\right) L_s \approx \omega_T L_s$$

$$G_{m,eff} = g_{m1}Q_{in} = \frac{g_{m1}}{\omega C_{gs}(R_s + \omega_T L_s)}$$

$$= \frac{\omega_T}{\omega R_s \left(1 + \frac{\omega_T L_s}{R_s}\right)} = \frac{\omega_T}{2\omega R_s}$$

Note:  $G_{m,eff}$  is independent of  $g_{m1}$ !

# **LNA Input Stage: Some Observations**

- As noted, overall stage transconductance is independent of device g<sub>m</sub> if resonant frequency and current density are held constant.

- □ Theoretically, may use arbitrarily narrow devices and still obtain the desired transconductance.

- If drain current noise were the only noise source, narrower devices would lead to monotonically decreasing noise.

- □ Since gain is fixed, noise figure approaches 0dB as device narrows. Power dissipation would also approach zero.

- Absurd conclusion of zero dB NF, zero power dissipation and nonzero gain should make one suspect that something is missing from the foregoing.

Narrowband CMOS RF Low-Noise Amplifiers

### **MOSFET Two-Port Noise Parameters**

$$\Box \qquad B_{opt} = -B_c = -\omega C_{gs} \left( 1 + \alpha |c| \sqrt{\frac{\delta}{5\gamma}} \right)$$

B<sub>opt</sub> is inductive, except for frequency behavior. Difficult to provide this behavior over a large bandwidth.

$$\Box \quad G_{opt} = \sqrt{\frac{G_u}{R_n} + G_c^2} = \alpha \omega C_{gs} \sqrt{\frac{\delta}{5\gamma} \left(1 - |c|^2\right)}$$

$$\Box \quad F_{min} = 1 + 2R_n \left[G_{opt} + G_c\right] \approx 1 + \frac{2}{\sqrt{5}} \frac{\omega}{\omega_T} \sqrt{\gamma \delta \left(1 - |c|^2\right)}$$

Note that F<sub>min</sub> = 0dB if gate and drain noise were fully correlated. The mere presence of noise sources does not necessarily imply nonzero NF.

Narrowband CMOS RF Low-Noise Amplifiers

### **MOSFET Two-Port Noise Parameters**

Consider only drain and induced gate current noise.

Then, the following two-port parameters apply:

| Parameter      | Expression                                                                  |

|----------------|-----------------------------------------------------------------------------|

| G <sub>c</sub> | ≈ 0                                                                         |

| B <sub>c</sub> | $\omega C_{gs} \left( 1 + \alpha  c  \sqrt{\frac{\delta}{5\gamma}} \right)$ |

| R <sub>n</sub> | $\frac{\gamma g_{d0}}{2} = \frac{\gamma}{\alpha} \cdot \frac{1}{g_m}$       |

| G <sub>u</sub> | $\frac{\delta\omega^2 C_{gs}^2 \left(1 -  c ^2\right)}{\frac{5g}{d0}}$      |

# **MOSFET Two-Port Noise Parameters**

#### □ Let's now compile a short table of F<sub>min</sub> values:

| $g_{m'} \omega C_{gs}$ | F <sub>min</sub> (dB) |

|------------------------|-----------------------|

| 20                     | 0.5                   |

| 15                     | 0.6                   |

| 10                     | 0.9                   |

| 5                      | 1.6                   |

- □ Numbers pessimistically assume that hot electron effects triple the mean-square noise densities.

- Even with such effects, achievable noise figures are very good.

- Question: How can these values be approached in practice?

T. Lee, Paul G. Allen Center for Integrated Systems

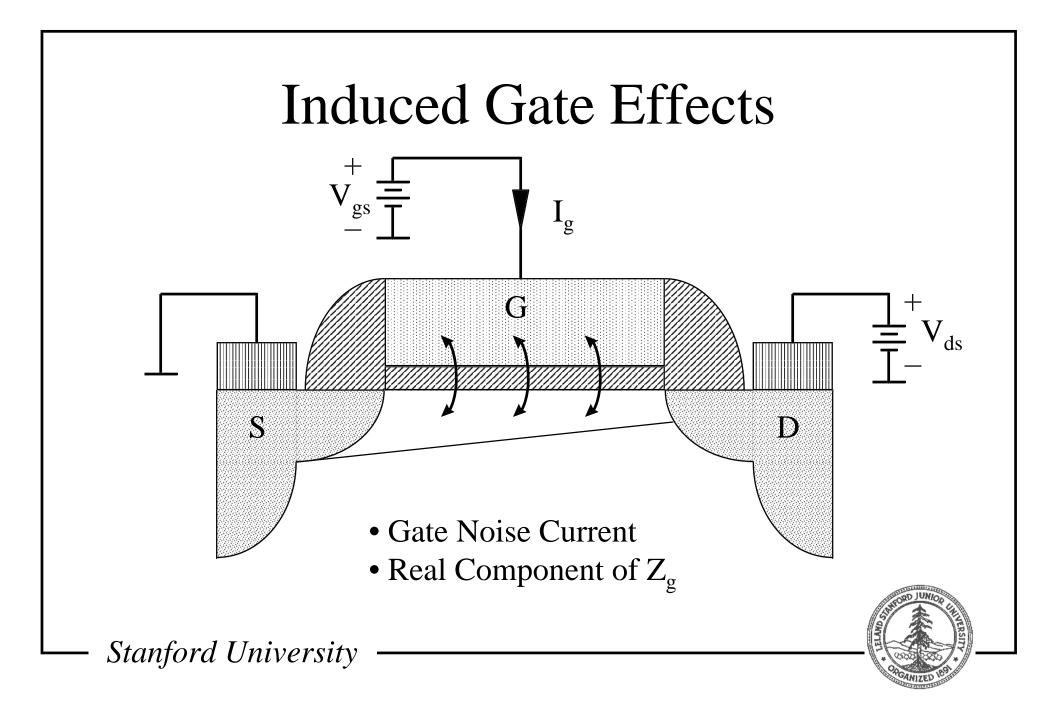

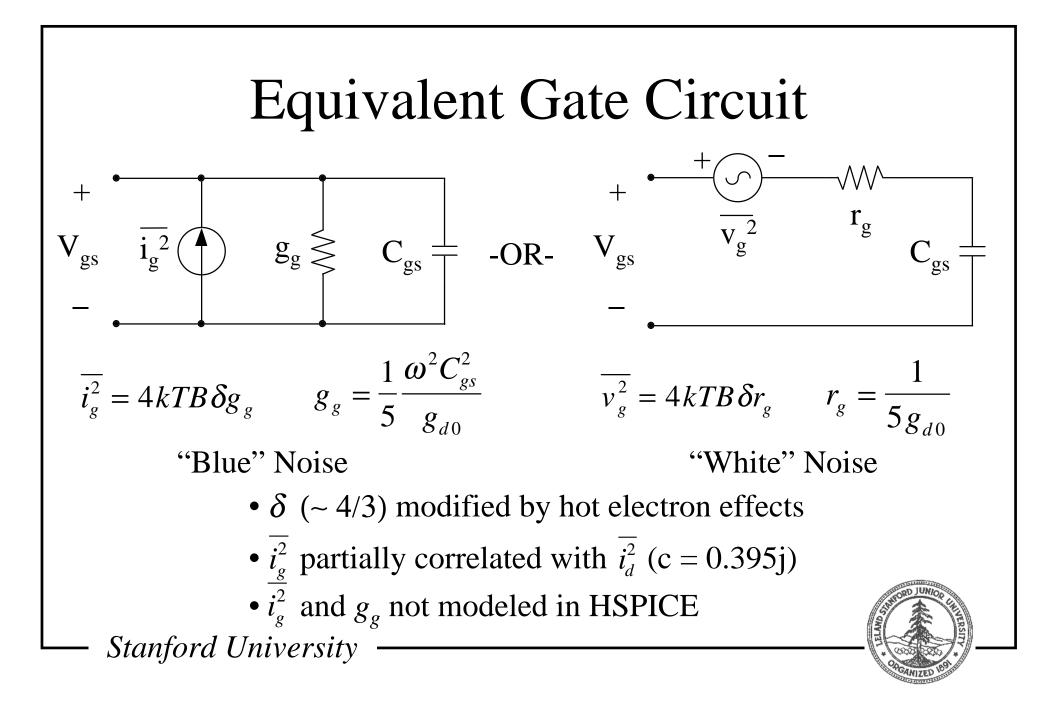

#### **Second-Order Noise Sources**

- Practical NF values are affected by series gate resistance and epi noise.

- **Γ** F is increased by  $R_g/R_s$ , so just 10Ω by itself sets a lower NF bound of 0.8dB in a 50Ω system.

- □ Must use multi-fingered devices (R<sub>finger</sub>= R<sub>SH</sub>W<sub>finger</sub>/3L).

- Cannot use planar spiral inductors in gate circuit if best NF is to be achieved (NF typically > 2-3dB).

- Thermal noise of substrate (epi) resistance modulates the back gate, giving rise to additional drain current noise:

$$\frac{i_{nd}^{2}}{\Delta f} = 4kT\left(\gamma g_{d0} + g_{mb}^{2}R_{epi}\right) = 4kTg_{d0}\left(\gamma + \frac{g_{mb}^{2}R_{epi}}{g_{d0}}\right)$$

Narrowband CMOS RF Low-Noise Amplifiers

#### **Second-Order Noise Sources**

**Effect of epi noise is equivalent to an increase in**  $\gamma$ **:**

$$\gamma_{eff} = \gamma + \frac{g_{mb}^2 R_{epi}}{g_{d0}}$$

- One may compute that, typically, epi noise increases γ by ~10%, an amount smaller than the uncertainty in γ itself.

- Epi noise also contributes to equivalent input current noise, but this is fully correlated with the drain noise.

- ☐ Again, fundamental NF limits are set by the *uncorrelated* gate and drain noise components.

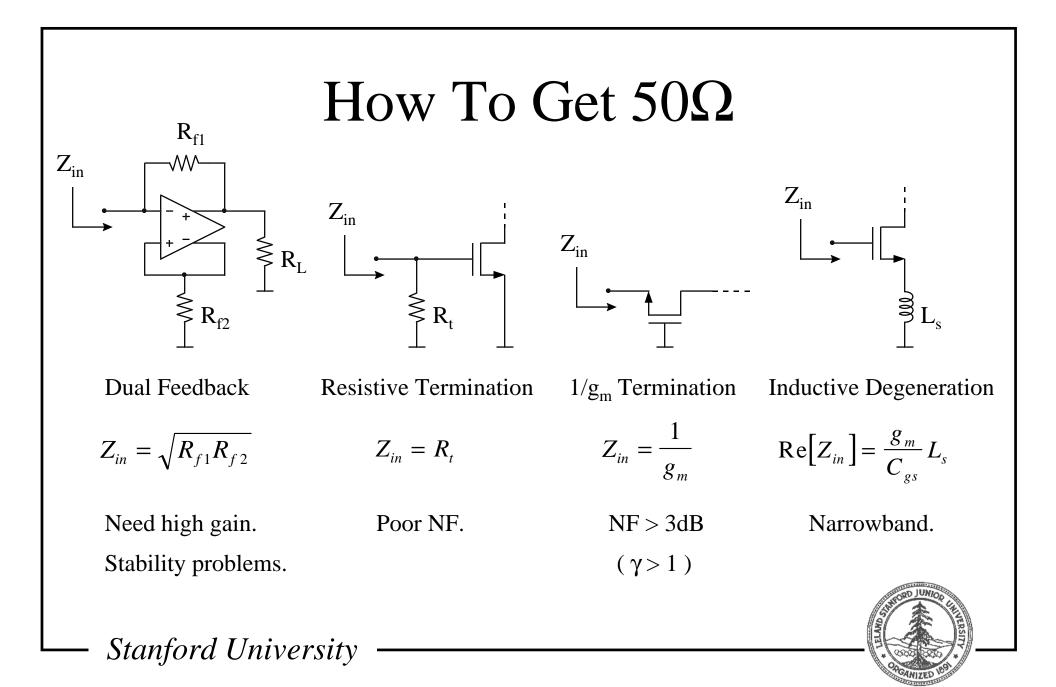

Choose inductive source degeneration to produce desired real part:

$$L_{S} \approx \frac{R_{S} \cdot \left[1 + 2\left(C_{gd} / C_{gs}\right)\right]}{\omega_{T}}$$

□ Equation assumes a cascode stack with equal-sized devices

- Choose sum of gate and source degenerating inductances either to resonate with C<sub>gs</sub> or to provide a susceptance equal to B<sub>opt</sub>.

- □ First choice maximizes gain, second choice minimizes NF. Difference is small because  $B_{opt} \approx \omega C_{gs}$ .

- Note that classic noise optimization says nothing about power dissipation, nor anything about how to select device width.

Narrowband CMOS RF Low-Noise Amplifiers

# **Power-Constrained Noise Optimization**

- **Good approximation: Select device width roughly equal to (500μm-GHz)/f**<sub>0</sub> (for a 50Ω system).

- □ Adjust bias to obtain desired power dissipation.

- ☐ Keep V<sub>DS</sub>-V<sub>DSAT</sub> as small as practical to minimize hot-electron effects (say, under half a volt or so).

- □ For equal-sized cascoding and main devices, continue to select source degeneration inductance according to:

$$L_{S} \approx \frac{R_{S} \cdot \left[1 + 2\left(C_{gd} C_{gs}\right)\right]}{\omega_{T}}$$

- $\Box \quad \text{Add gate inductance to bring input to resonance.}$

- **□** Noise factor bound is  $1 + 2.4(\gamma/\alpha)(\omega/\omega_T)$ , so scaling continues to help directly.

# **Experimental Results: Devices**

- □ For 0.5µm technology (drawn), NF<sub>min</sub> ≈ 1.0dB @ 2mA, 1GHz.

- □ NF<sub>min</sub> decreases to  $\approx$  0.7dB @ high I<sub>D</sub>.

- □ NF<sub>min</sub> increases to  $\approx$  1.3dB @ 2GHz @ high I<sub>D</sub>.

- **□** NF<sub>min</sub> still below 2dB @ 400µA, 1GHz.

- □ These values apply to a single device without regard for input impedance.

- □ Practical NF<sub>min</sub> values are perhaps 0.5dB to 1dB higher.

- Contrary to expectations, no increase in NF<sub>min</sub> is observed in these devices as V<sub>DS</sub> increases in saturation.

- □ Drain engineering possibly responsible (G. Klimovitch et al., 1997).

Narrowband CMOS RF Low-Noise Amplifiers

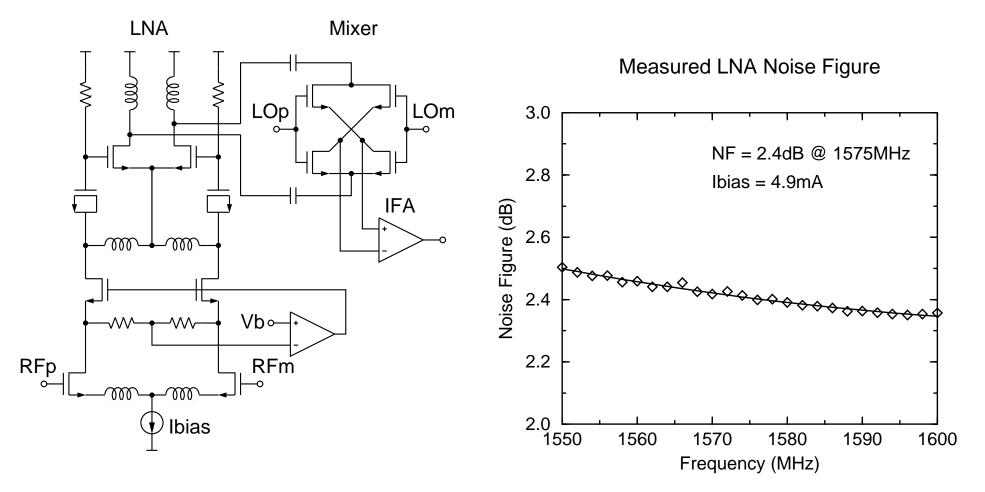

## **Experimental Results: Circuits**

- Single-ended versions consume half the power for a given NF than differential versions, but:

- **☐** No rejection of common-mode noise.

- □ Very sensitive to parasitics, particularly inductances in the source lead of the main transistor.

- Differential versions are relatively insensitive to hardto-model and hard-to-control parasitics.

- □ Attractive for high-volume production.

- Common-mode rejection highly desirable for mixed-signal environments.

#### CIRCUITS: LNA / MIXER

Shahani, Shaeffer and Lee, "A 12mW Wide Dynamic Range CMOS GPS Receiver," ISSCC 1997

# **Experimental Results: Circuits**

- Series gate inductance provided by bondwires to avoid inevitable NF degradation associated with spiral inductors.

- Difficult to obtain accurate value without trimming, but repeatability with automated die attach and bonding equipment is very good.

- □ Input Q is generally 3-5, so LNA is somewhat forgiving of moderate element value variation.

- □ Measured and simulated NF agree to within 0.2dB.

- □  $S_{11} < -15 dB.$

- □ Receiver IIP3 > -16dBm (measurement confounded by linearity limitation of subsequent receiver stages).

- □ IIP3 > -6dBm for LNA itself (simulated).

# **Summary and Conclusions**

- CMOS devices are capable of excellent noise performance in the low-GHz frequency range.

- ❑ Noise performance will continue to improve, despite fears that hot-electron effects will nullify the benefits of scaling.

- □ Inductively-degenerated LNA architecture simultaneously provides near-optimum gain and NF.

- **Proper device width is important, also.**

- □ At under 10mW dissipation, practical single-ended amplifier noise figures of ~1.5dB at 1GHz are achievable with 0.5µm technology.

- □ Short-channel effects improve linearity, so dynamic range per power will improve with scaling.

- Epi and gate resistance noise effects are minor, or can be made so.

Narrowband CMOS RF Low-Noise Amplifiers

# Acknowledgments

- Derek Shaeffer, for studying this topic as part of his Ph.D. thesis work at Stanford.

- Gabriel Brenna, for making many device NF measurements as part of his Diploma Thesis work (joint Stanford-École Polytechnique Fédérale de Lausanne).

- Dr. Natalino Camilleri of Advanced Micro Devices, for supplying the test devices, and making test facilities available.

- □ Ernie McReynolds of Tektronix, for incorporating gate noise into simulator device models for us.

- □ Dr. Christopher Hull of Rockwell International, for assistance in fabricating the GPS receiver.