Session FP 16: Paper 16.6

## **Fractal Capacitors**

#### Hirad Samavati, Ali Hajimiri, Arvin R. Shahani, Gitty N. Nasserbakht<sup>1</sup>, Thomas H. Lee

Stanford University, Stanford, CA

<sup>1</sup>Texas Instruments, Dallas, TX

# Outline

- Motivation

- Fractal capacitors

- CAD tool

- Measurements

- Conclusions

### **Motivation**

- Demand for linear capacitors

- Area efficiency

- Improvement with process scaling

- Reduction of bottom-plate capacitance

## **Traditional Capacitors**

#### • Gate Capacitance:

High capacitance per unit area Nonlinear Requires DC bias voltage Low breakdown voltage Medium Q

#### • Junction Capacitance:

Highly nonlinear Requires DC bias voltage Sensitive to process variations Low Q Large temperature variation

#### • Metal to Metal / Poly Capacitance:

Linear High Q Small temperature variation Low capacitance per unit area

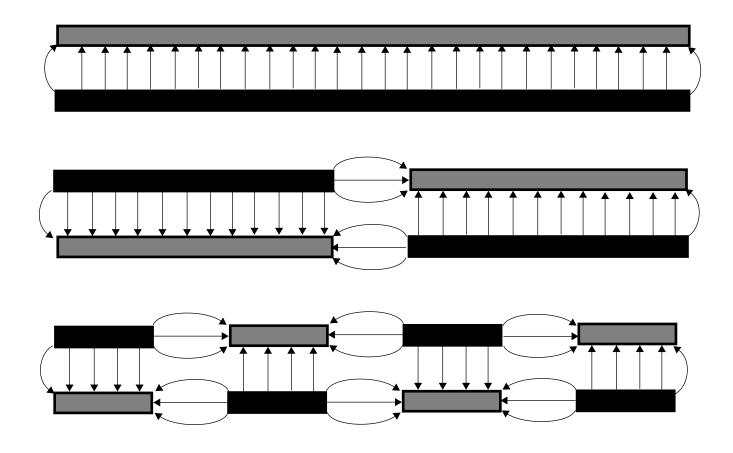

### Vertical vs. Lateral Flux

• Lateral flux increases the total amount of capacitance.

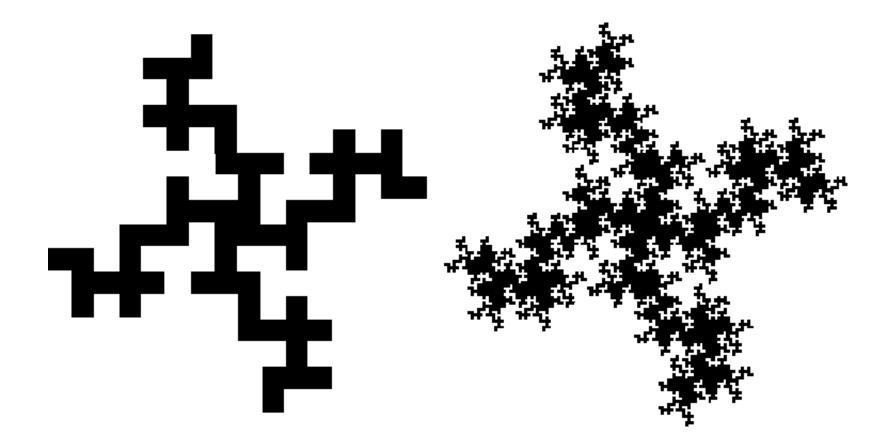

### **Fractal Geometries**

• Some fractals have finite area but infinite perimeter.

## **Fractal Capacitor**

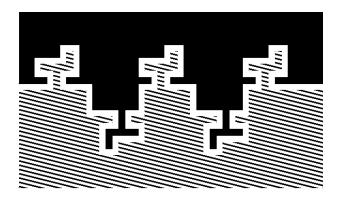

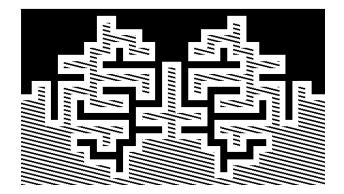

Quasi fractal geometries can be utilized to increase capacitance per unit area.

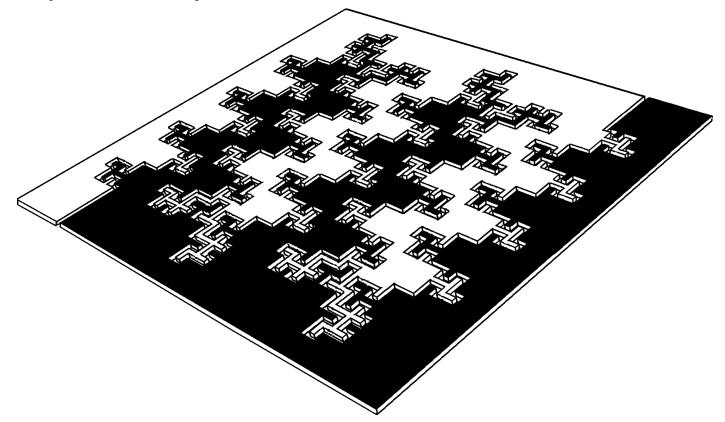

3-D representation of a fractal capacitor using a single metal layer.

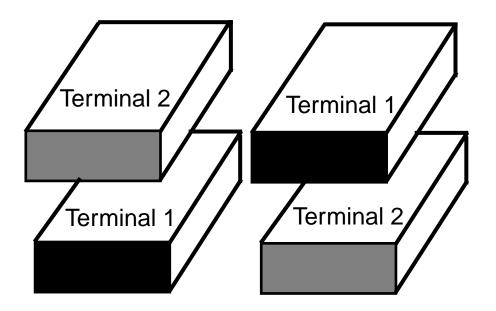

#### Layout Issues

Cross connection

• Fractal dimension

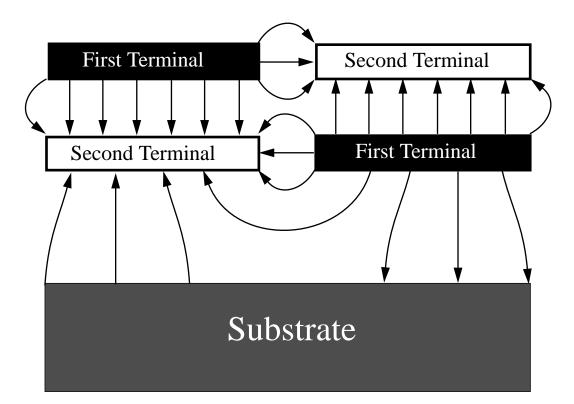

## Reduction of the Bottom-Plate Capacitance

- Area is smaller.

- Some of the field lines terminate on the adjacent plate instead of the substrate.

# Scaling

Unlike conventional parallel-plate structures, the capacitance per unit area increases as the process technologies scale.

# **Other Advantages**

- Lateral flux capacitors shift the burden of matching away from oxide thickness to lithography.

- The effect of systematic lithography offset is reduced due to pseudo-random nature of the structure.

- Capacitance density can be traded for lower series resistance.

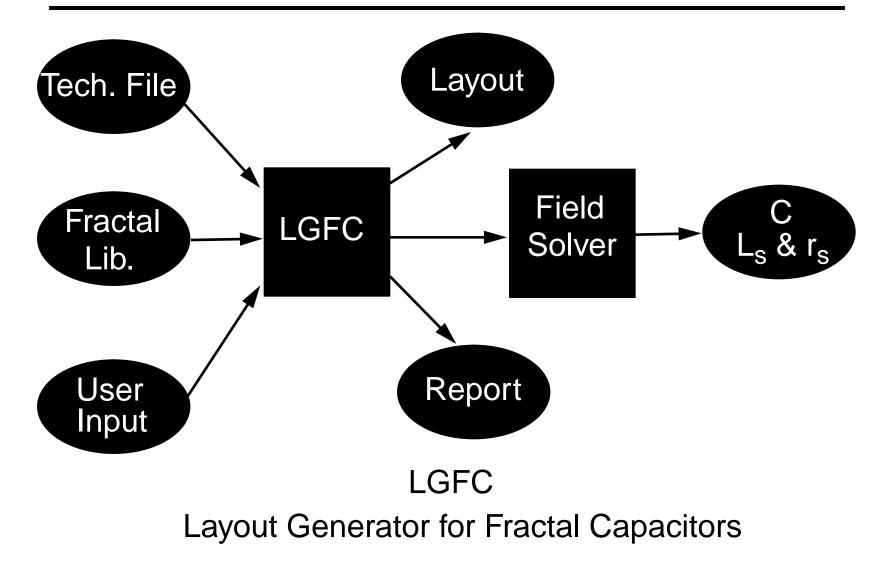

# CAD Tool

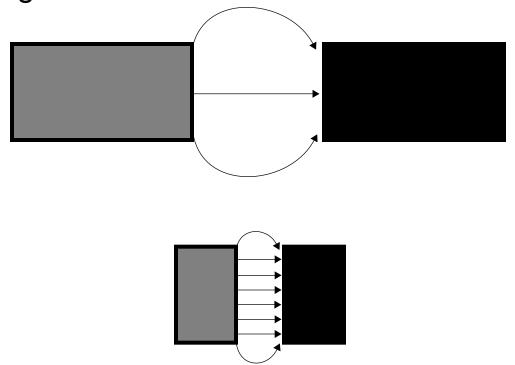

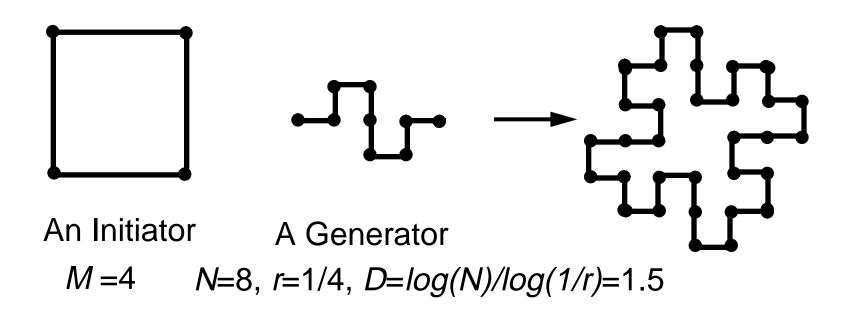

# Fractal Construction: An Example

- Choose an "initiator."

- Replace each segment of the initiator by a "generator."

- Continue recursively.

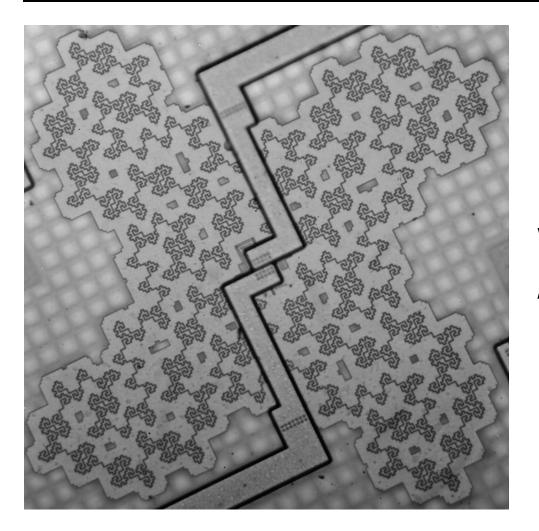

## Die Micrograph

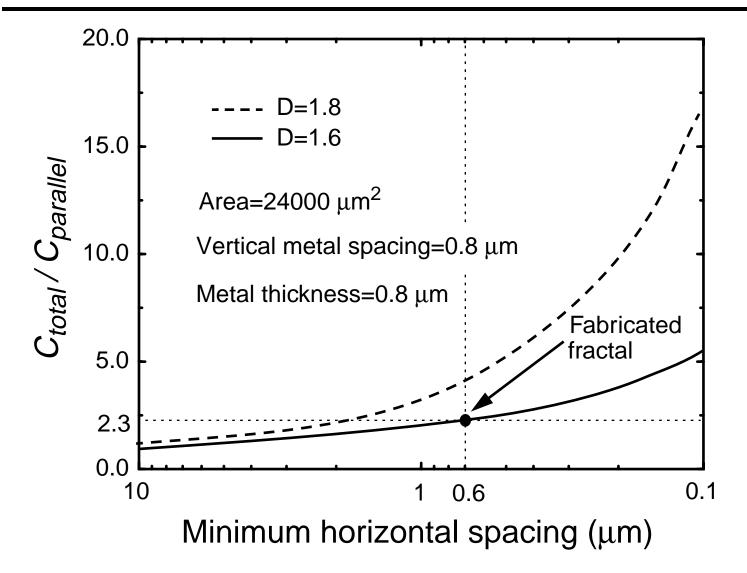

Horizontal spacing=0.6  $\mu$ m Vertical spacing=0.8 $\mu$ m Area=24,000  $\mu$ m<sup>2</sup>

### **Capacitance Estimation**

$$C_{lateral} = K \frac{(\sqrt{A})^{D}}{(w+s)^{D-1}} \times t$$

- w: Minimum width of the metal.

- *s*: Minimum spacing between two adjacent strips.

- A: Area of the fractal capacitance.

- *t*: Thickness of the metal layers.

- K: Proportionality factor that depends on the family of fractals being used.

- D: Fractal dimension.

#### Boost Factor vs. Lateral Spacing

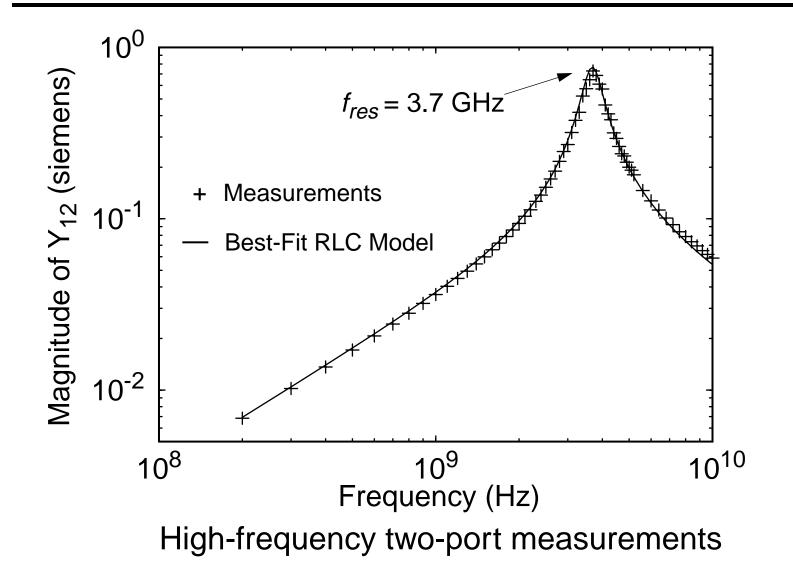

#### Measurements

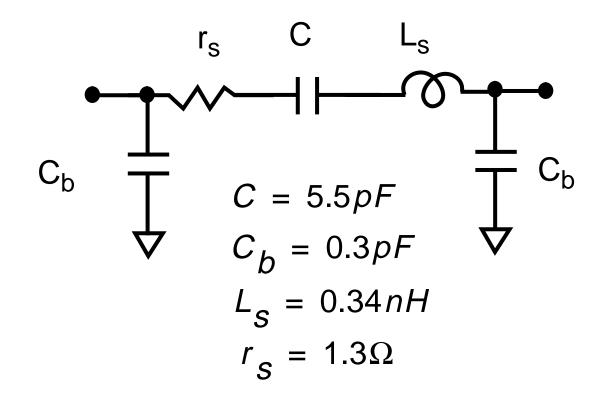

**Best-Fit Parameters**

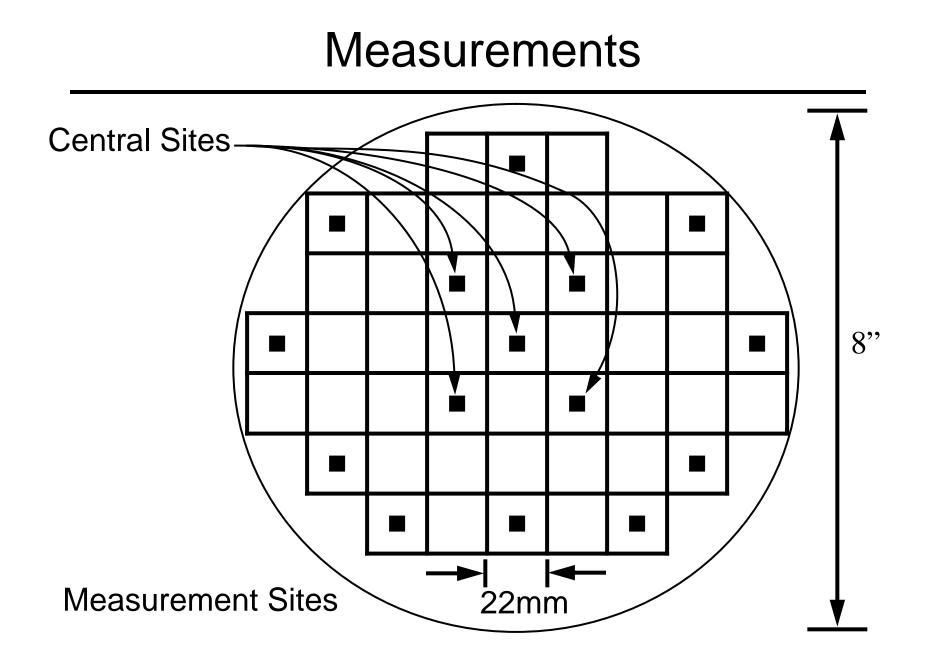

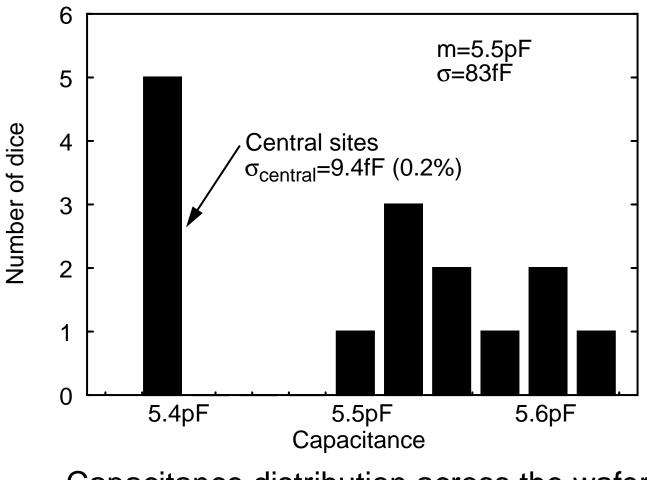

#### Measurements

Capacitance distribution across the wafer

- There is a good agreement between the measurements (5.5pF mean) and the simulations (5.4pF).

- 90% of the measured series inductance is due to connecting stubs.

- About 80% of the series resistance can be attributed to vias and connecting stubs.

- Both series resistance and inductance are dominated by non fundamental mechanisms.

- The overall improvement over a standard parallel plate capacitor is a factor of 2.3.

### Conclusions

- Fractal capacitors use chip area more efficiently.

- Fractal capacitors are linear.

- The capacitance density improves with the scaling of process technologies.

- Bottom-plate parasitic capacitance is reduced.

- A CAD tool to automatically generate custom fractal layouts has been developed.