October 29, 1997

Rafael J. Betancourt Zamora

Center for Integrated Systems

Department of Electrical Engineering

Stanford University

- Introduction

- Frequency Synthesizer Design

- Phase Noise Theory

- Voltage-controlled Oscillator Design

- Simulation and Measured Results

- Conclusion and Acknowledgements

# **Biotelemetry is Crucial for Space Life Sciences**

- On the ground, animals can be housed separately for data collection, and tethered systems are feasible. In space, where volume is very costly, animals must be group-housed, making tethers undesirable.

- *In vivo* experiments often require anesthetized animals and hard-wired connections to the implant, creating a risk of infection due to transcutaneous leads.

- NASA-Ames Research Center is developing the Advanced BioTelemetry System (ABTS) to conduct space-based animal research.

- Implantable biotelemetry supports real-time data gathering. It allows experiments with awake and unrestrained animals, and eliminates problems with lead breakage, movement artifacts, and ground loops.

- NASA needs a low power implantable transmitter that can relay biosensor data using the 174-216MHz band.

## **Human Applications for Biotelemetry**

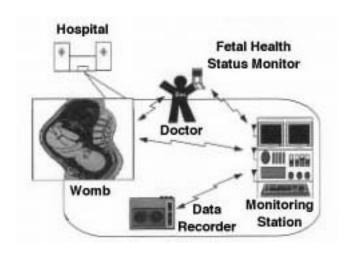

- NASA researchers are collaborating with doctors at the University of California-San Francisco's (UCSF) Fetal Treatment Center to adapt space biosensor and biotelemetry technology for the monitoring of fetuses with life-threatening congenital conditions.

- At UCSF's Fetal Treatment Center there is a need for telemetry of physiological parameters of human fetuses for monitoring and identifying distress after surgery.

- A telemetry implant that will monitor heart rate, temperature, pH, and amniotic fluid pressure is required to operate in utero for up to 3 months.

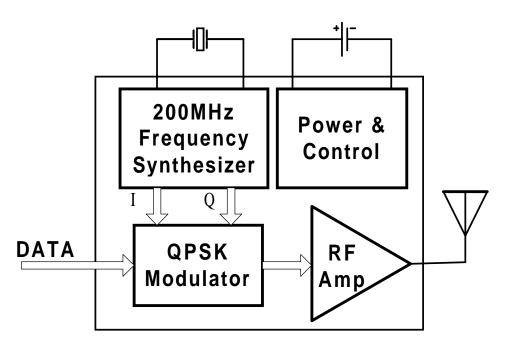

# **Goal: An Implantable Biotelemetry Transmitter**

- Frequency: 174-216MHz

- Data Rate: 100 kbps

- Modulation: Quadrature Phase Shift Keying (QPSK)

- Range: 1 meter

- Power source: 3.6 V, 750mAH lithium

- Implant lifetime: 100 hours (continuous)

- Implant volume: 5 cm<sup>3</sup> (including battery)

Our goal is to design and build a low-power radio transmitter in CMOS suitable for short range biosensor and implantable use.

- Introduction

- Frequency Synthesizer Design

- Phase Noise Theory

- Voltage-controlled Oscillator Design

- Simulation and Measured Results

- Conclusion and Acknowledgements

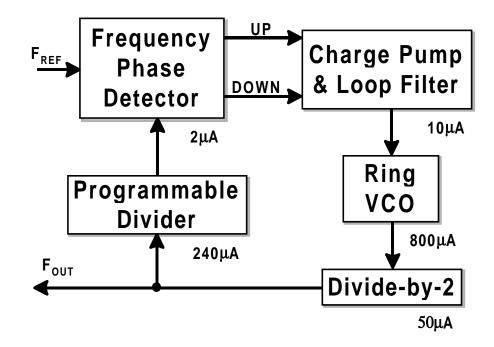

## Phase-locked Loop Frequency Synthesizer

- The most important parameter of an implanted biotelemetry system is power dissipation.

- A significant portion of the power budget is allocated to the generation of the RF carrier.

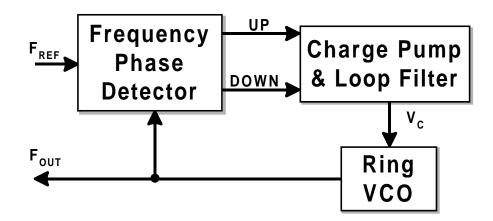

- Traditionally, frequency synthesizers have been implemented using phase-locked loops (PLLs).

- The major sources of power dissipation are the VCO (73%) and the frequency divider (22%).

Power budget for a typical CMOS PLL frequency synthesizer used in microprocessor clock generation<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>V. Kaenel, et al., "A 320MHz, 1.5mW at 1.35V CMOS PLL for Microprocessor Clock Generation", *Intl. Solid-State Circuits Conference*, Feb. 1996, pp.132-133.

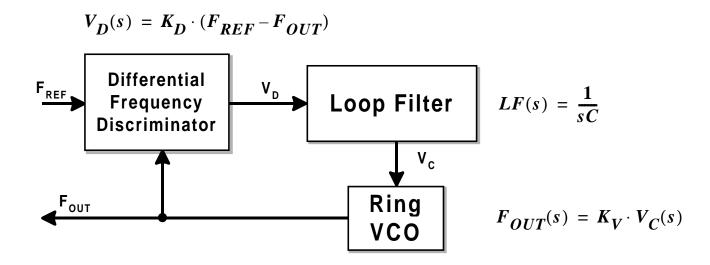

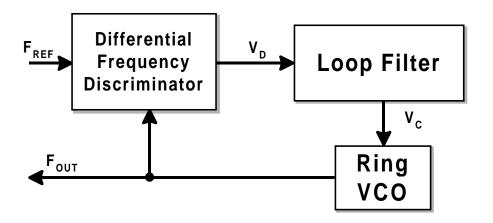

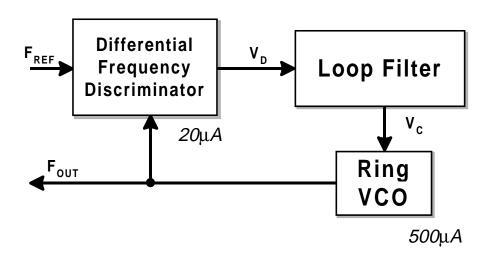

# Frequency-locked Loop Frequency Synthesizer

• Closed loop response:

• where  $\omega_N$  (rad/s) is the loop bandwidth

$$\frac{F_{OUT}}{F_{REF}}(s) = \frac{1}{1 + s/\omega_N} \qquad \omega_N = \frac{K_V \cdot K_D}{C}$$

A linear analysis using a single pole filter shows that this is a first order system, and thus inherently stable (neglecting sampled-data effects).

# **FLL vs. PLL Frequency Synthesizers**

$$\frac{F_{OUT}}{F_{REF}}(s) = \frac{1}{1 + s/\omega_N}$$

$$\frac{\Theta_{OUT}}{\Theta_{REF}}(s) = \frac{\omega_n^2 + 2\zeta\omega_n s}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

The controlled variable in a FLL is frequency not phase.

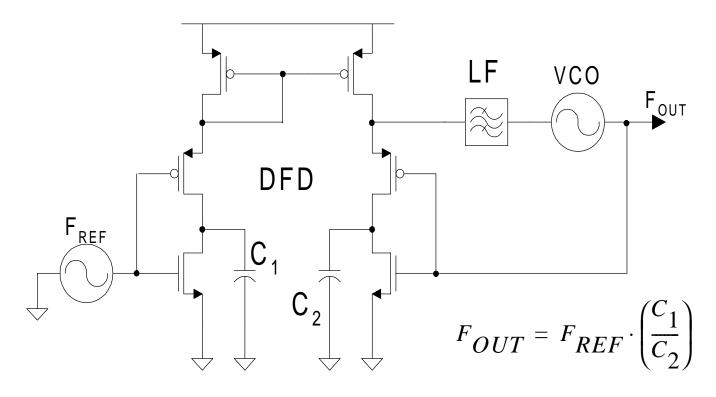

## **Differential Frequency Discriminator**

- This FLL does not require a frequency divider, which represents 22% of the power budget for the PLL example just shown.

- The FLL can perform frequency comparison directly without a divider by using a DFD implemented with switched capacitor circuits.

- The output frequency is determined by the capacitor ratio, C<sub>1</sub>/C<sub>2</sub>, and the reference frequency.

# **Power Dissipation vs. Phase Noise**

- In a synthesizer application, the reference frequency source is usually a crystal oscillator with very low phase noise.

- A PLL tracks the phase noise of the reference signal, relaxing the close-in phase noise requirements of the VCO.

- However, a FLL tracks the VCO's frequency, not phase, forcing more stringent requirements on the VCO.

- The VCO's power dissipation is determined by the frequency of operation and the phase noise performance required.

- In biotelemetry, data rates are low (10-100kbps), and channel spacing wide (3MHz), relaxing the phase noise requirements for the VCO.

- Introduction

- Frequency Synthesizer Design

- Phase Noise Theory

- Voltage-controlled Oscillator Design

- Simulation and Measured Results

- Conclusion and Acknowledgements

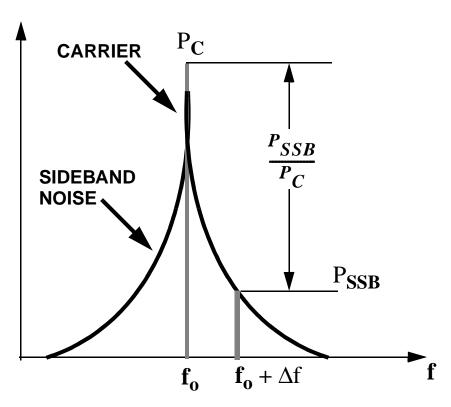

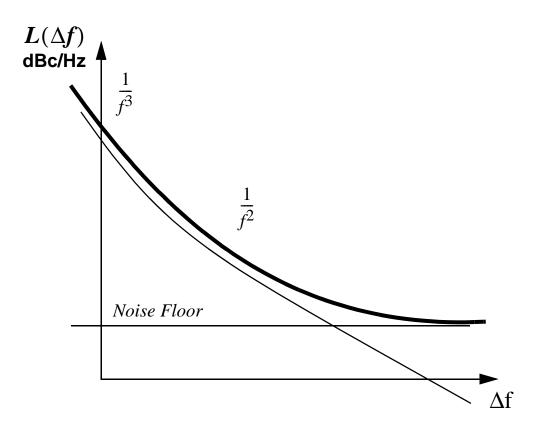

#### What is Phase Noise?

- The output power of an oscillator is not concentrated exclusively at the carrier frequency alone.

- The spectral distribution on either side of the carrier is known as spectral sidebands.

- Phase noise power is represented as a ratio of power in 1Hz bandwidth in one sideband to the power of the carrier.

- This ratio is specified in units of dBc/Hz at some frequency offset from the carrier.

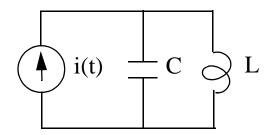

## **Oscillators are Time-Variant Systems**

A current impulse injected at the peak only changes the amplitude and has no effect on the phase.

A current impulse injected at the zerocrossing only changes the phase and has minimal effect on the amplitude.

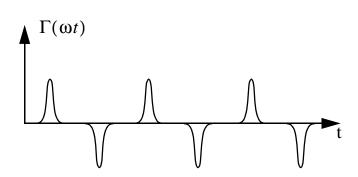

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0 \tau)}{q_{max}} u(t-\tau)$$

- where the Impulse Sensitivity Function  $\Gamma(x)$  is a periodic function.

- and q<sub>max</sub> is the maximum charge displacement in the tank.

## Impulse Sensitivity Function for Ring Oscillators

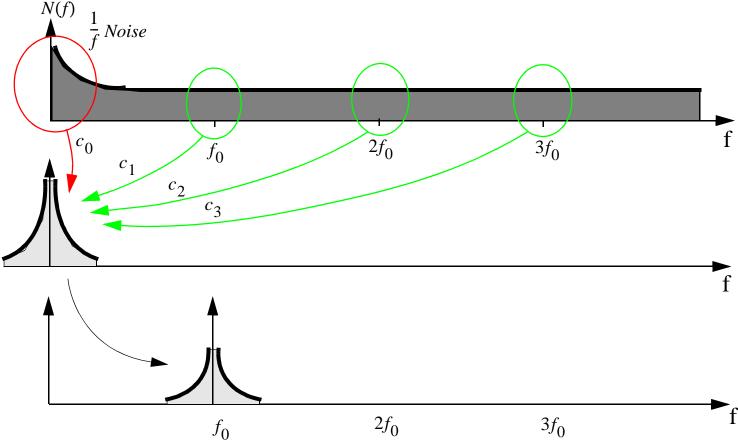

$$\phi(t) = \frac{1}{q_{max}} \left[ \frac{c_0}{2} \int_{-\infty}^{t} i(\tau) d\tau + \sum_{n=1}^{\infty} c_n \int_{-\infty}^{t} i_n(\tau) \cos(n\omega \tau) d\tau \right]$$

- $\Gamma(x)$  can be calculated directly from the waveform.

- Since  $\Gamma(x)$  is periodic, it may be expressed as a Fourier series, and used in a superposition integral to determine the phase noise spectrum resulting from known device and circuit noise<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>T. Lee, "CMOS RF: No Longer an Oxymoron", IEEE GaAs IC Symp., Oct. 1997, pp.244-247.

## **Upconversion of Device 1/f Noise**

- Phase noise close to the carrier results from the folding of device noise centered at integer multiples of the carrier frequency.

- The upconversion of device 1/f noise occurs through  $c_0$ , the DC value of the ISF.

- The DC value of the ISF is governed by the symmetry properties of the waveform.

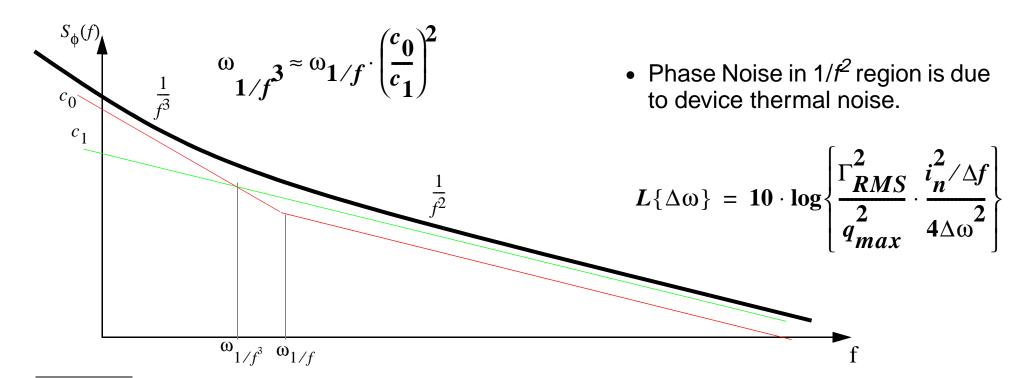

# Hajimiri Phase Noise Model<sup>2</sup>

- Phase Noise in  $1/f^3$  region is due to device 1/f noise.

- It is commonly assumed that the  $1/f^3$  corner of phase noise is the same as the 1/f corner of the device noise spectrum. This is NOT the case.

<sup>&</sup>lt;sup>2</sup>A. Hajimiri, T. Lee, "A General Theory of Phase Noise in Oscillators", *IEEE Journal of Solid-State Circuits (in press)*.

- Introduction

- Frequency Synthesizer Design

- Phase Noise Theory

- Voltage-controlled Oscillator Design

- Simulation and Measured Results

- Conclusion and Acknowledgements

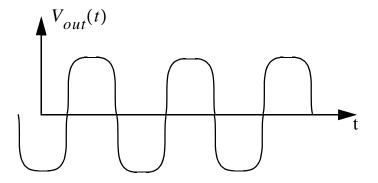

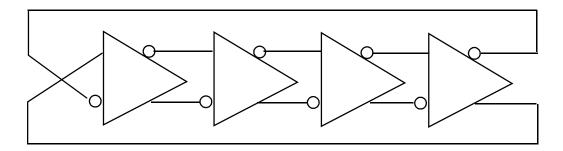

# **Voltage-controlled Oscillator Design**

- The VCO design is critical in the performance of the FLL synthesizer as the phase noise at the output of the FLL is solely a function of the phase noise of the VCO.

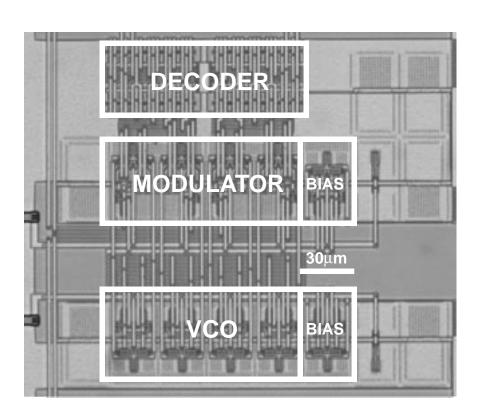

- The VCO consists of a 4-stage differential ring oscillator<sup>3</sup>.

- Frequency control is achieved by changing the biasing of the buffer stages which determines the delay through each cell.

<sup>&</sup>lt;sup>3</sup> A.W. Buchwald, K.W.Martin, "High Speed Voltage Controlled Oscillators with Quadrature Outputs", *Electronics Letters*, 14 Feb. 1991, Vol. 27 No. 4, pp.309-310.

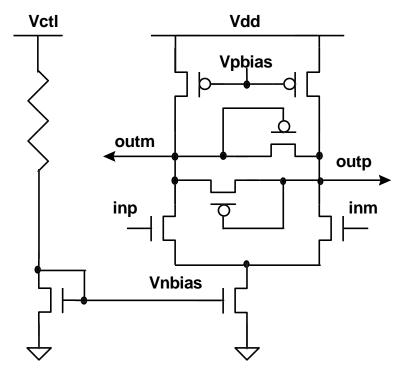

## **Differential Delay Buffer Design**

- The differential buffers used have been shown to have excellent noise and power supply rejection characteristics<sup>4</sup>.

- The layout of the ring oscillator is symmetrical and load balanced to avoid any skewing between the phases.

<sup>&</sup>lt;sup>4</sup> M. Horowitz, et al., "PLL Design for a 500MB/s Interface", Intl. Solid-State Circuits Conference, Feb. 1993, pp.160-161.

# Phase Noise Analysis of Ring Oscillator VCO

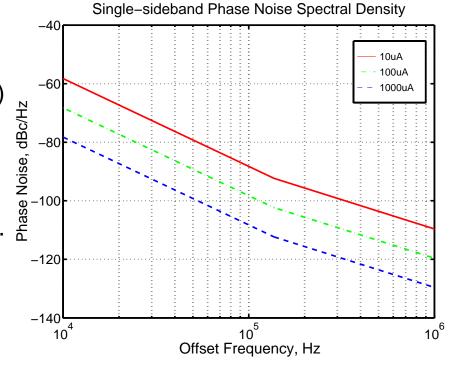

$$L\{\Delta\omega\} = 10 \cdot \log \left\{ \frac{64kT}{I_{DD}^{E} C^{L}_{EFF}} \left( \frac{f_{o}^{2}}{\Delta\omega^{2}} \right) \right\}$$

Single-sideband phase noise (dBc/Hz) for a differential ring oscillator in the 1/f<sup>2</sup> region

- I<sub>DD</sub> is the tail current of a single stage

- E<sub>C</sub> is the critical field (e.g., 4.918 V/μm)

- L<sub>EFF</sub> is the gate length of the differential-pair devices (e.g., 0.5μm)

- We selected the 100μA curve, for a total current drain of 500μA at 200MHz.

- Introduction

- Frequency Synthesizer Design

- Phase Noise Theory

- Voltage-controlled Oscillator Design

- Simulation and Measured Results

- Conclusion and Acknowledgements

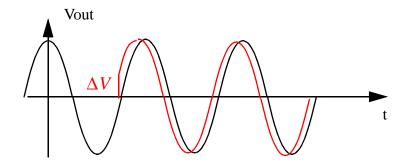

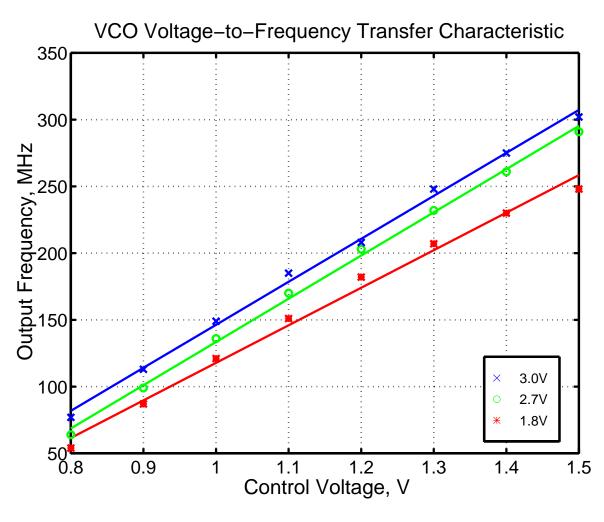

## Test Results: VCO Transfer Characteristic

- Fabricated through MOSIS using the HP 0.5μm CMOS process.

- The VCO voltage-tofrequency transfer characteristic was measured for different supply voltages.

- Tuning Range: 350kHz-707MHz @3V

- VCO Gain = 321MHz/V @3V

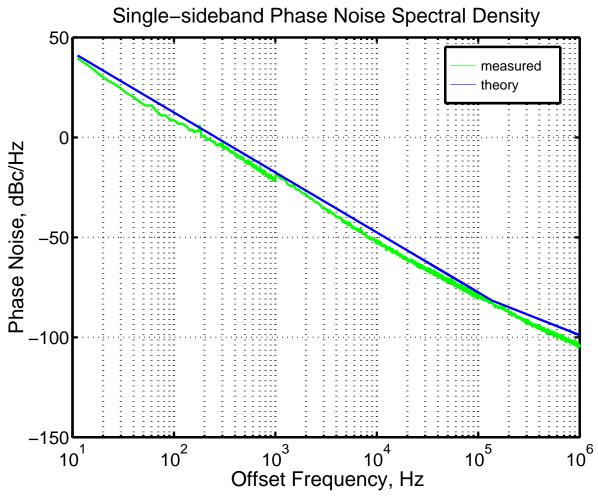

#### **Test Results: Phase Noise**

- Using an HP8590B spectrum analyzer, the phase noise was measured at -82dBc/Hz for 100kHz offset from a 200MHz carrier.

- These measurements are within 2dB of the predicted values for frequency offsets between 10Hz and 1MHz.

Test results using RDI's NTS-1000A phase noise measurement test set, along with the theoretical phase noise performance predicted by the Hajimiri model (f<sub>c</sub>=150.9MHz).

- Introduction

- Frequency Synthesizer Design

- Phase Noise Theory

- Voltage-controlled Oscillator Design

- Simulation and Measured Results

- Conclusion and Acknowledgements

## **Conclusions**

- The frequency-locked loop (FLL) synthesizer imposes more stringent phase noise requirements on the VCO.

- A design technique using the Hajimiri phase noise model was presented.

- A 200MHz ring oscillator VCO was designed and fabricated in 0.5μm CMOS.

- Measurements of phase noise show good agreement with the theory.

# **Acknowledgements**

- This work was partially supported by NASA-Ames Research Center through a Training Grant No. NGT 2-52211.

- We gratefully acknowledge the support of John W. Hines, manager of the Sensors 2000! program at NASA-Ames Research Center.