### Recent Developments in CMOS RF Integrated Circuits

Prof. Thomas H. Lee Stanford University tomlee@ee.stanford.edu http://www-smirc.stanford.edu

T. Lee, Paul G. Allen Center for Integrated Systems

Recent Developments in CMOS RF Integrated Circuits

#### Introduction

- Digital CMOS is hardly the ideal medium for RF ICs. But is it hopelessly inferior?

- □ Interesting question: How well can one do in such a technology if one tries very hard?

- Scaling delivers faster devices every year; eventually, they'll be fast enough.

- □ Is the substrate really so big a problem that good inductors (and capacitors) simply cannot be realized?

- □ Is device noise so large that CMOS LNAs will always be HNAs?

- Does the inferior 1/f noise of CMOS transistors doom the close-in phase noise performance of oscillators?

- Can you *really* build credible RF ICs in standard digital CMOS?

#### Outline

- □ A few brief words on scaling trends

- □ The patterned ground shield spiral inductor

- **Capacitors**

- ☐ Fractal capacitors

- □ Accumulation mode varactors

- Passive mixers

- □ Broadband noise models for the deep submicron regime

- Power-constrained LNA design

- □ A new phase noise theory and its implications for 1/f noise upconversion

- □ Putting it all together: A 115mW single chip GPS receiver in 0.5µm CMOS

Recent Developments in CMOS RF Integrated Circuits

#### **Scaling Trends in Brief**

- □ CMOS f<sub>T</sub> (and f<sub>max</sub>) are in the range of 30GHz now, and double roughly every three years.

- □ Devices with ~75nm L<sub>eff</sub> have been demonstrated, and exhibit ~150GHz f<sub>T</sub>!

- CMOS suffers from large source/drain parasitics, compared with other technologies.

- ☐ Gate-drain "overlap" capacitance is also large.

- Series gate resistance is also an increasingly serious problem as gate lengths continue to shrink, but can be accommodated by using narrower unit devices.

- □ Salicided gates help, too.

- □ Interconnect layers increasing at ~0.75 to 1 level per generation (5 layers are now relatively common).

#### **Passive Elements: Planar Spiral Inductors**

- Planar spirals in Si technology are infamous for poor Q (typically well below 10).

- Conductor resistance, exacerbated by skin and proximity effects, typically accounts for about half the loss.

- ❑ Applies to both bulk and epi technologies.

- □ The remaining loss is primarily due to currents flowing in the substrate.

- □ Getting rid of the substrate would work wonders (e.g., postfab etch, SOA, etc.), but requires deviation from ordinary process technology.

- Next-best choice is to use a high-resistivity substrate, but can't do so without sacrificing other CMOS characteristics.

- □ Next next-best choice is to construct a *pseudo-substrate* out of existing interconnect layers.

#### **Passive Elements: Planar Spiral Inductors**

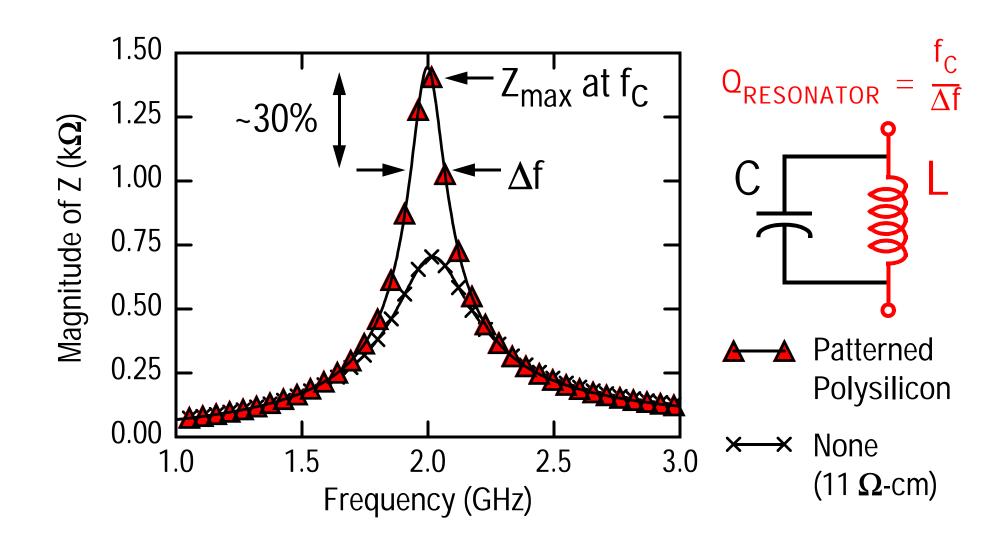

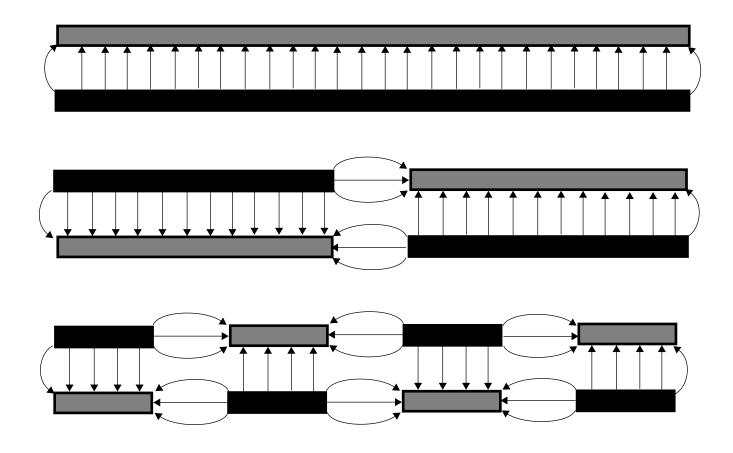

- Most of the substrate loss is *not* due to the flow of magnetically induced eddy currents, contrary to widespread superstition.

- Main mechanism is simply current flow into the substrate through the parasitic capacitance between inductor and substrate.

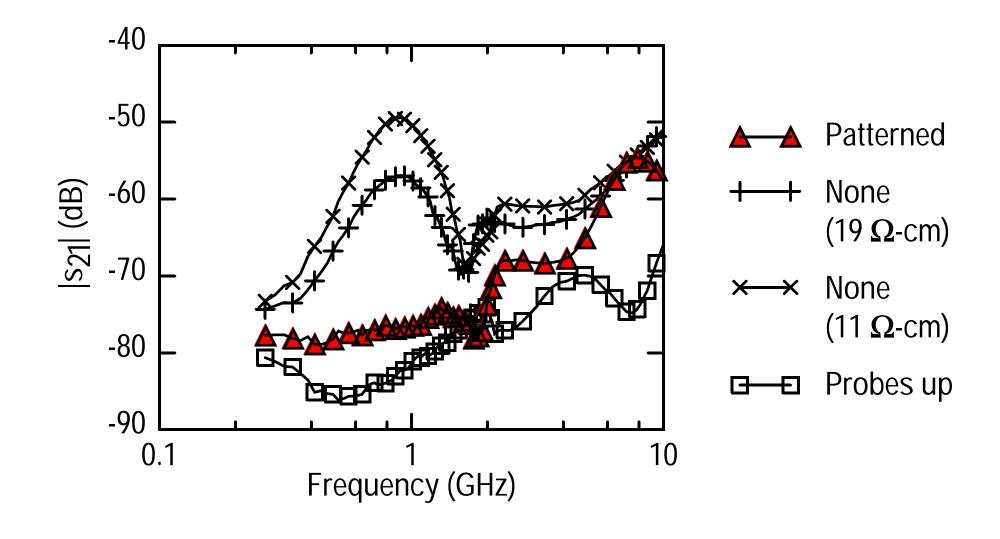

- □ Grounded shield interposed between inductor and substrate diverts this current into ground.

- □ Slots cut into ground shield prevent loss in shield due to eddy currents.

- Drawback is a reduction in self-resonant frequency due to increase in parasitic capacitance (can mitigate this by using higher-level metal layers).

http://holst.stanford.edu/~CPYue

yuechik@holst.stanford.edu

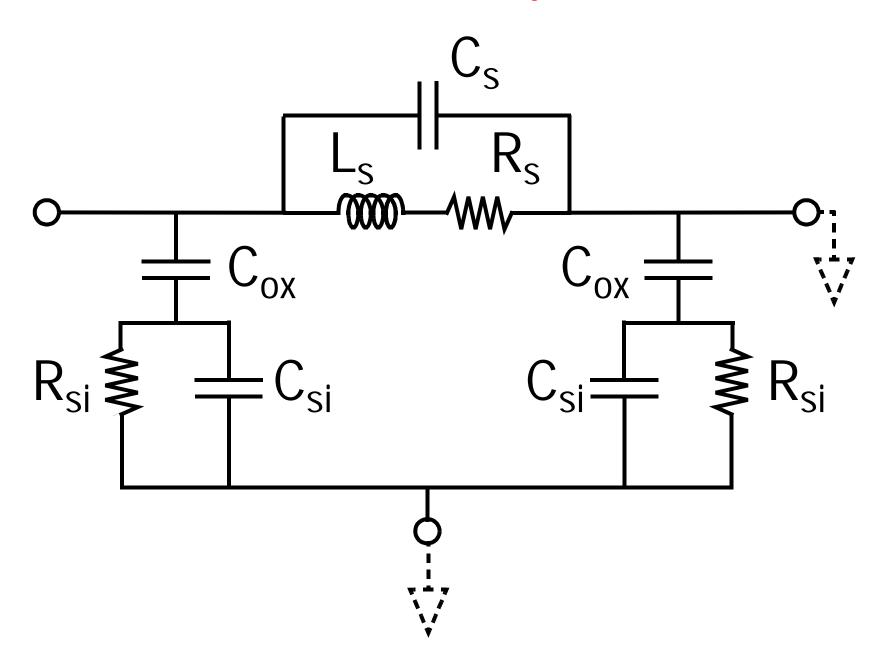

# **Model Description**

# **Model Description**

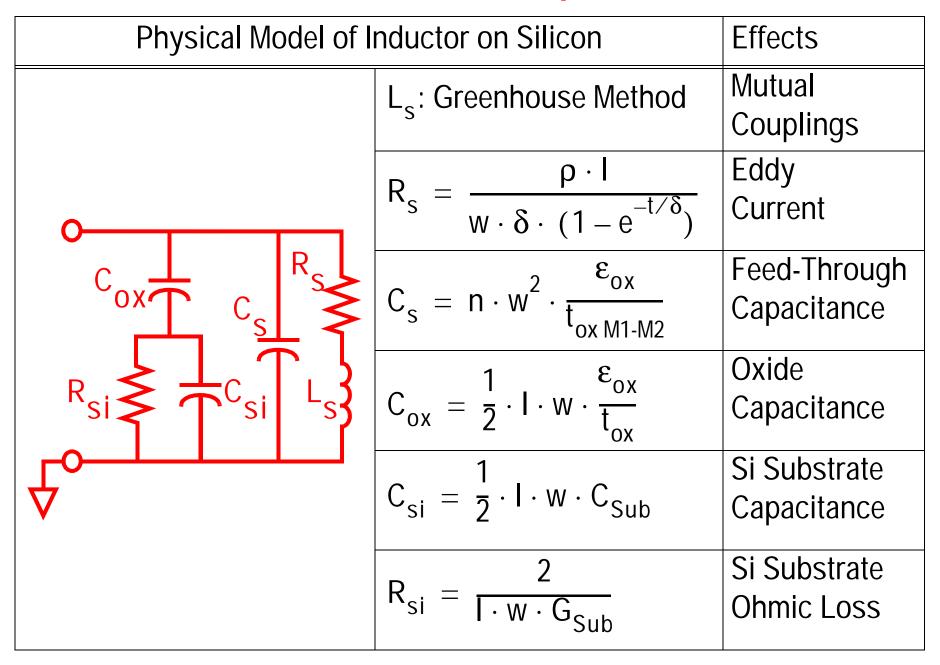

# Contour Plots of Q

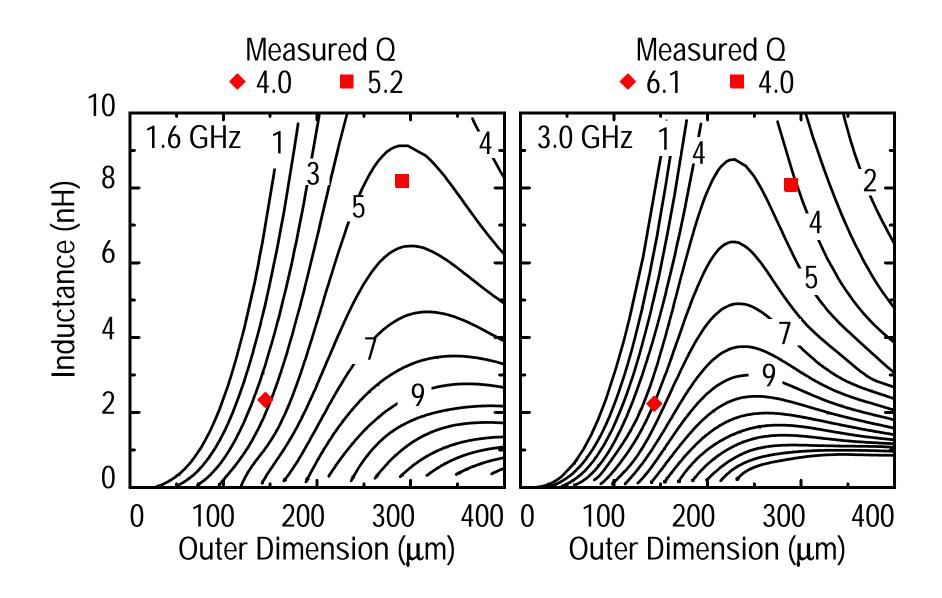

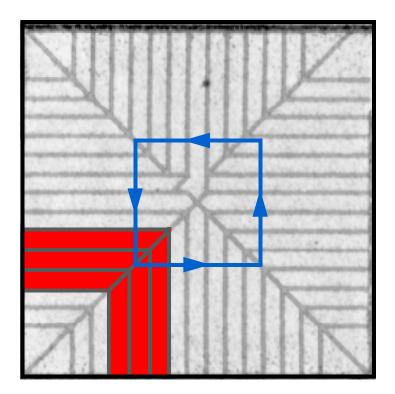

# Patterned Ground Shield Design

- Pattern

- Orthogonal to spiral (induced loop current)

- Resistance

- Low for termination of the electric field

- Avoid attenuation of the magnetic field

- Ground Strips

- Slot between Strips

- Induced Loop Current

# Parallel LC Resonator at 2 GHz

http://holst.stanford.edu/~CPYue

yuechik@holst.stanford.edu

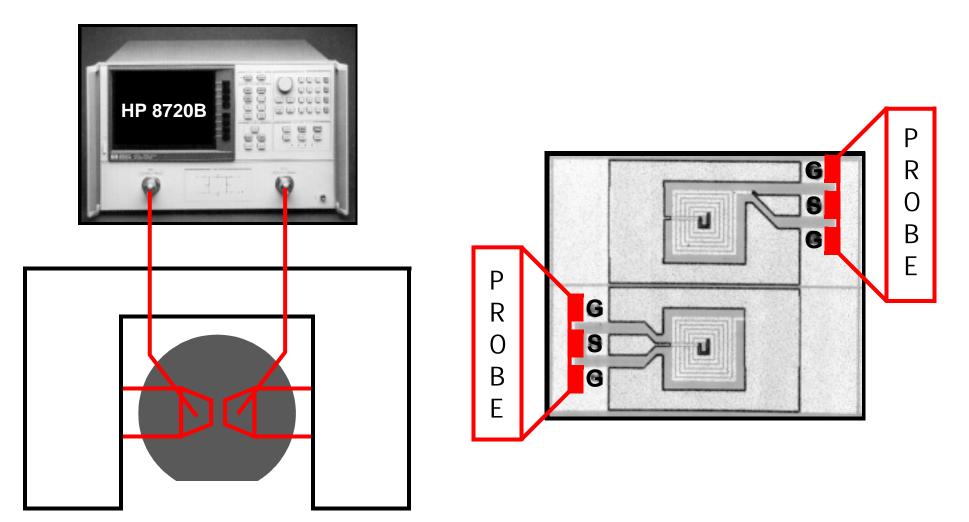

# Noise Coupling Measurement

**Probe Station**

http://holst.stanford.edu/~CPYue

yuechik@holst.stanford.edu

# Effect of Polysilicon GS on Isolation

#### **Passive Elements: Capacitors**

- Ordinary parallel plate structures don't scale with technology because the vertical spacing is held roughly constant to keep interconnect capacitance small.

- □ Bottom-plate parasitics are large (e.g., 30% of main capacitance).

- □ Gate capacitors are area efficient, but impose bias constraints, and are not as linear as MIM structures.

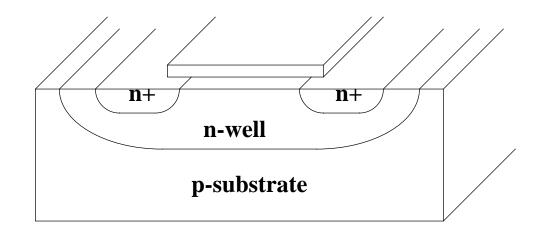

- □ Traditional varactor options (e.g., p+ in n-well) have poor Q

- □ Gate capacitors in accumulation-mode are an attractive alternative (Q values in excess of 100 at 1GHz are potentially realizable)

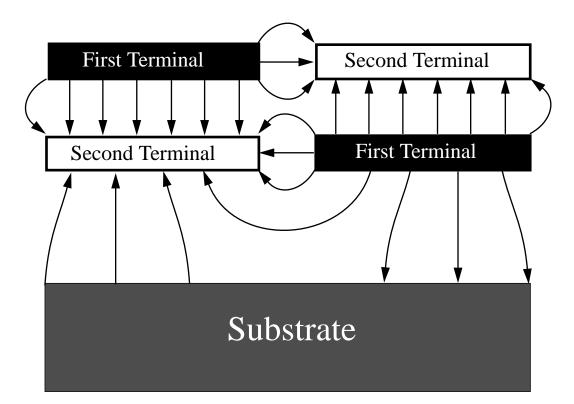

#### Vertical vs. Lateral Flux

• Lateral flux increases the total amount of capacitance.

### Reduction of the Bottom-Plate Capacitance

- Area is smaller.

- Some of the field lines terminate on the adjacent plate instead of the substrate.

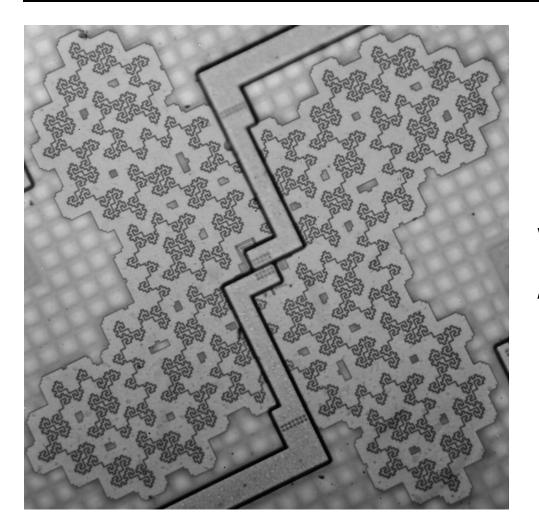

#### Die Micrograph

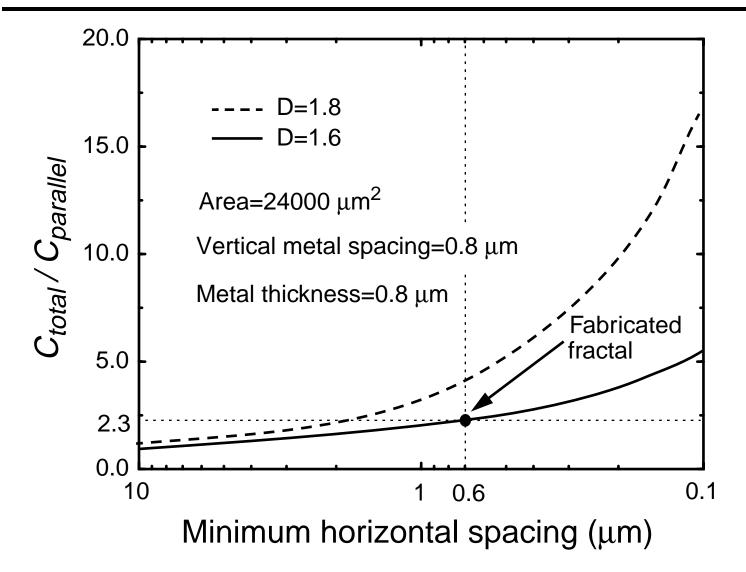

Horizontal spacing=0.6  $\mu$ m Vertical spacing=0.8 $\mu$ m Area=24,000  $\mu$ m<sup>2</sup>

#### Boost Factor vs. Lateral Spacing

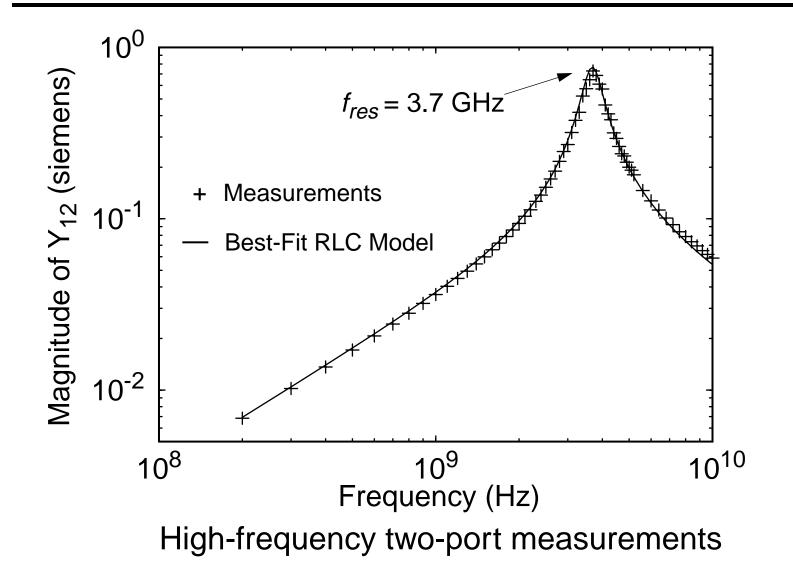

#### Measurements

**Best-Fit Parameters**

#### **Passive Elements: Capacitors**

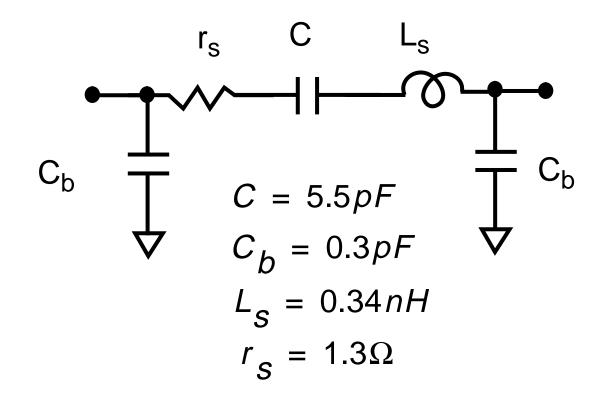

Accumulation-mode varactor (ref. Soorapanth et al., VLSI Circuits Symposium, June 1998):

Compatible with standard CMOS processing

Practical capacitance range exceeds 150%

**Recent Developments in CMOS RF Integrated Circuits**

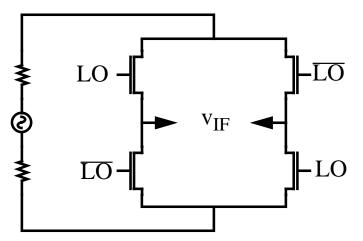

- Gilbert multiplier performs mixing in current domain because bipolar transistors are not good voltage switches.

- □ Penalty: V-I conversion costs power and linearity

- □ CMOS voltage switches are excellent, so mixers made out of them work well:

□ @1.6GHz: 3.6dB loss, +10dBm IIP3 achieved at 200µW

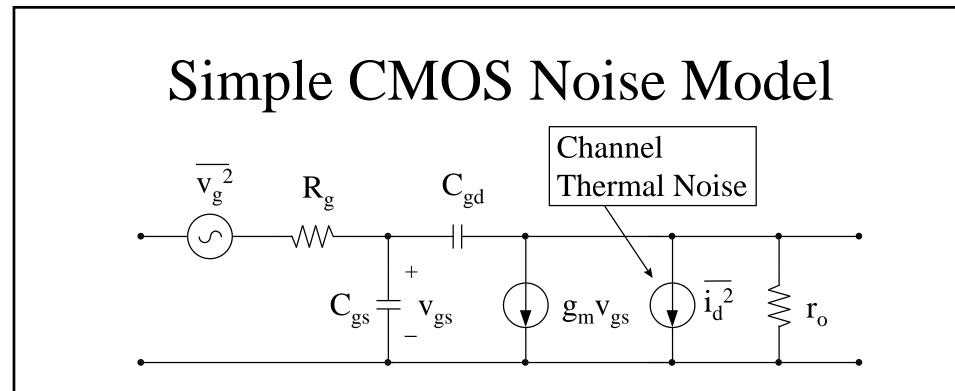

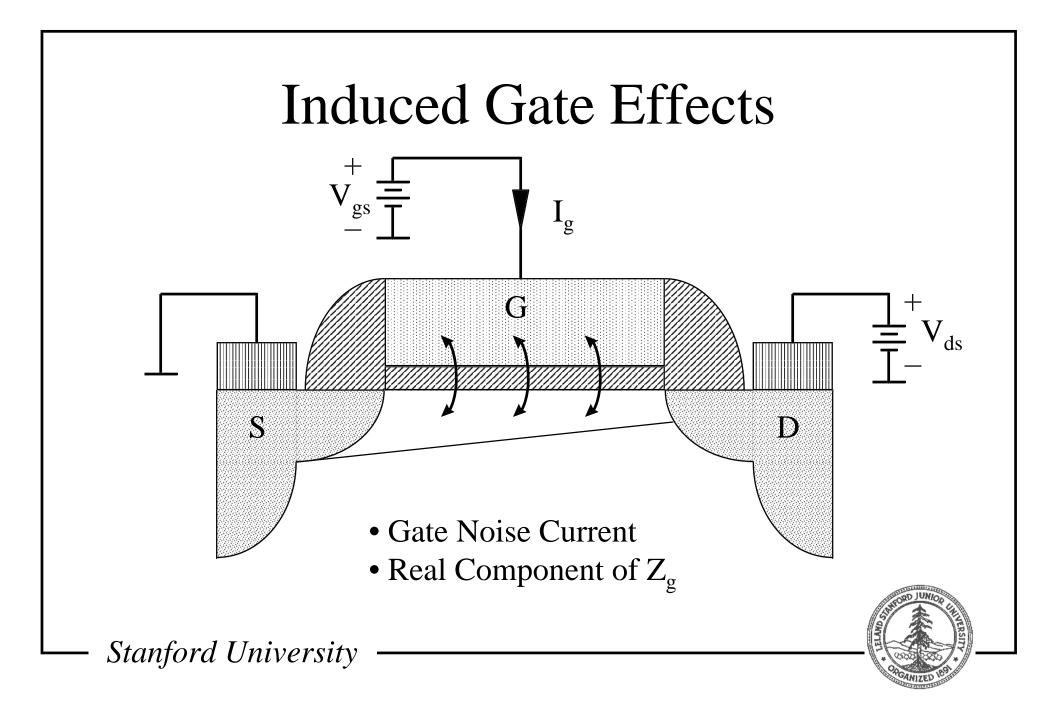

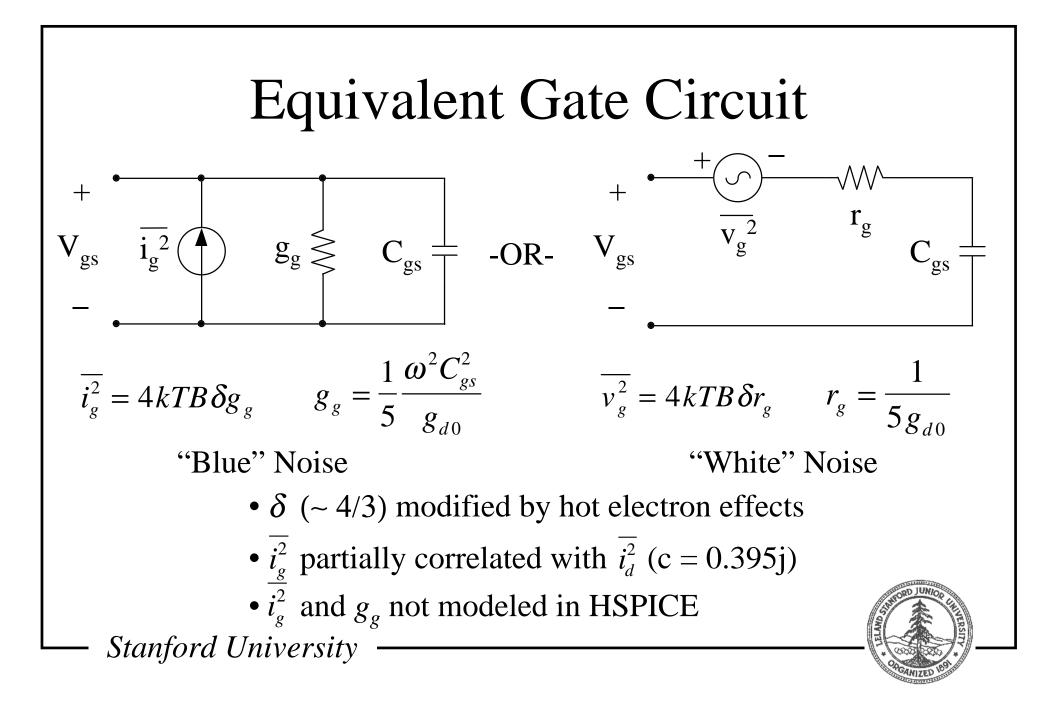

• Channel thermal noise is dominant.

$$\overline{i_d^2} = 4kTB\gamma g_{d0}$$

• Gate resistance minimized by good layout.

Stanford University

LNA Input Stage

$$Z_{in} = s(L_s + L_g) + \frac{1}{sC_{gs}} + \left(\frac{g_m}{C_{gs}}\right) L_s \approx \omega_T L_s$$

$$G_{m,eff} = g_{m1}Q_{in} = \frac{g_{m1}}{\omega C_{gs}(R_s + \omega_T L_s)}$$

$$= \frac{\omega_T}{\omega R_s \left(1 + \frac{\omega_T L_s}{R_s}\right)} = \frac{\omega_T}{2\omega R_s}$$

Note:  $G_{m,eff}$  is independent of  $g_{m1}$ !

#### **LNA Design Procedure**

- **Select device width roughly equal to (500µm-GHz)/f**<sub>0</sub> (for a 50Ω system)

- □ Adjust bias to obtain desired power dissipation

- ☐ Keep V<sub>DS</sub>-V<sub>DSAT</sub> as small as practical to minimize hot-electron effects (say, under half a volt or so)

- Select source degeneration inductance (assuming equalsized cascoding and main devices) according to:

$$L_{S} \approx \frac{R_{S} \cdot \left[1 + 2\left(C_{gd}/C_{gs}\right)\right]}{\omega_{T}}$$

Add enough gate inductance to bring input to resonance

Noise factor bound is 1 + 2.4(γ/α)(ω/ω<sub>T</sub>), so scaling continues to help directly

Recent Developments in CMOS RF Integrated Circuits

T. Lee, Paul G. Allen Center for Integrated Systems

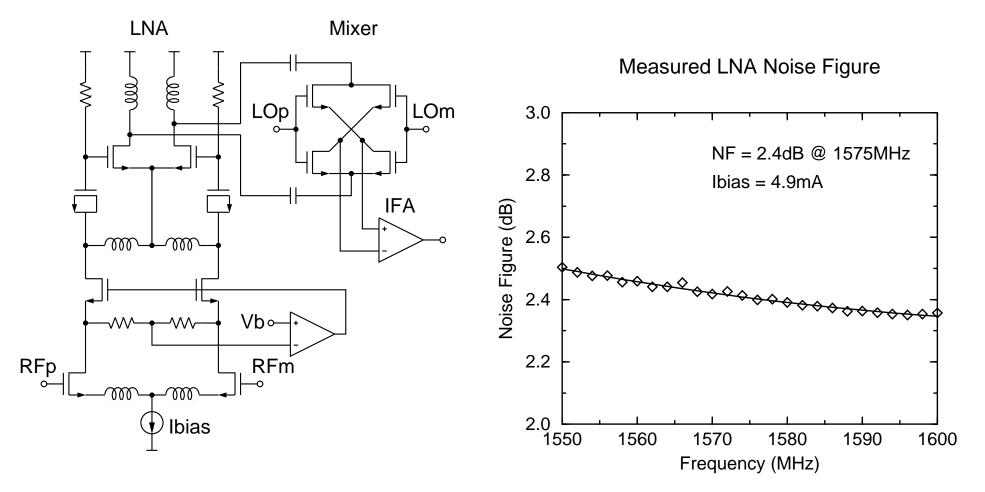

#### CIRCUITS: LNA / MIXER

Shahani, Shaeffer and Lee, "A 12mW Wide Dynamic Range CMOS GPS Receiver," ISSCC 1997

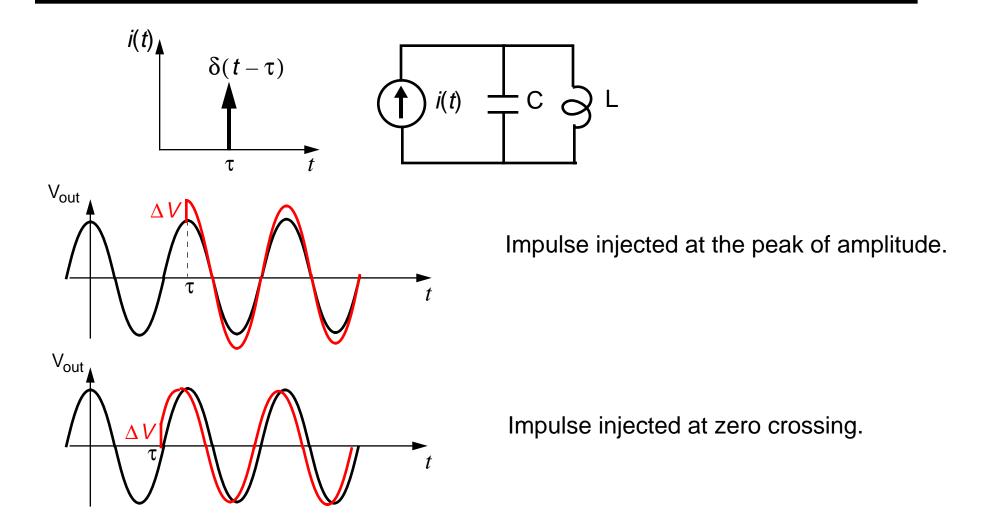

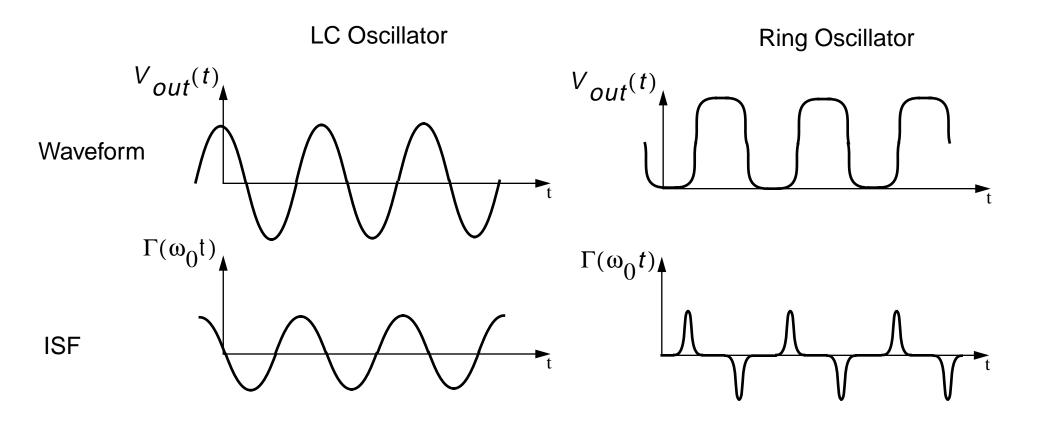

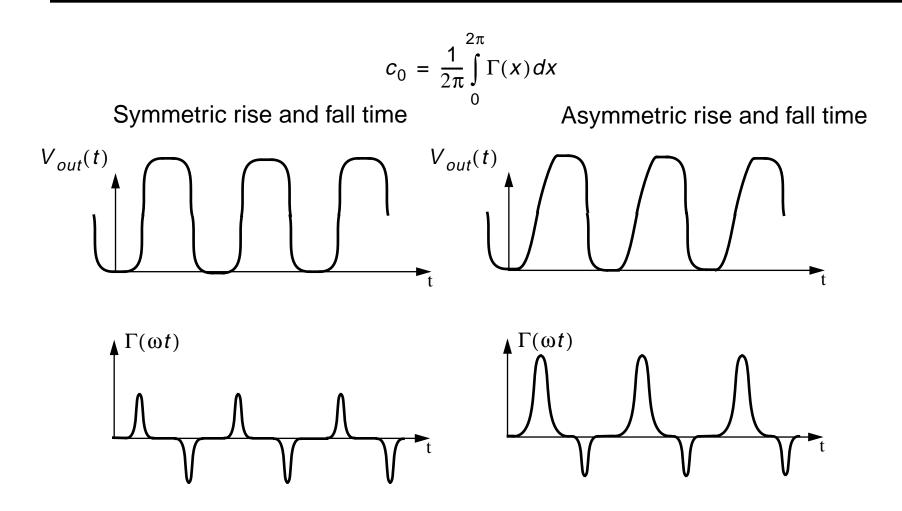

### **Oscillators Are Time-Variant Systems**

Even for an ideal LC oscillator, the phase response is *Time Variant.*

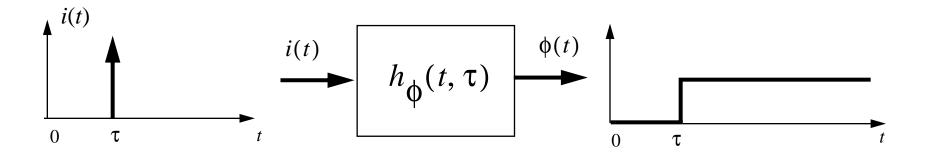

### Phase Impulse Response

The phase impulse response of an arbitrary oscillator is a time varying step.

The unit impulse response is:

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_o \tau)}{q_{max}} u(t-\tau)$$

$\Gamma(x)$  is a dimensionless function periodic in  $2\pi$ , describing how much phase change results from applying an impulse at time:  $t = T \frac{x}{2\pi}$

## Impulse Sensitivity Function (ISF)

The ISF quantifies the sensitivity of every point in the waveform to perturbations.

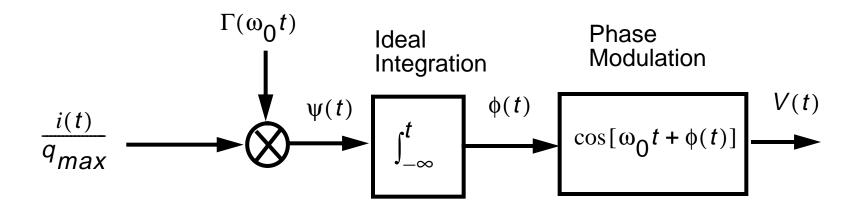

## Phase Response to an Arbitrary Source

Superposition Integral:

$$\phi(t) = \int_{-\infty}^{\infty} h_{\phi}(t,\tau) i(\tau) d\tau = \frac{1}{q_{max}} \int_{-\infty}^{t} \Gamma(\omega_{0}\tau) i(\tau) d\tau$$

Equivalent representation:

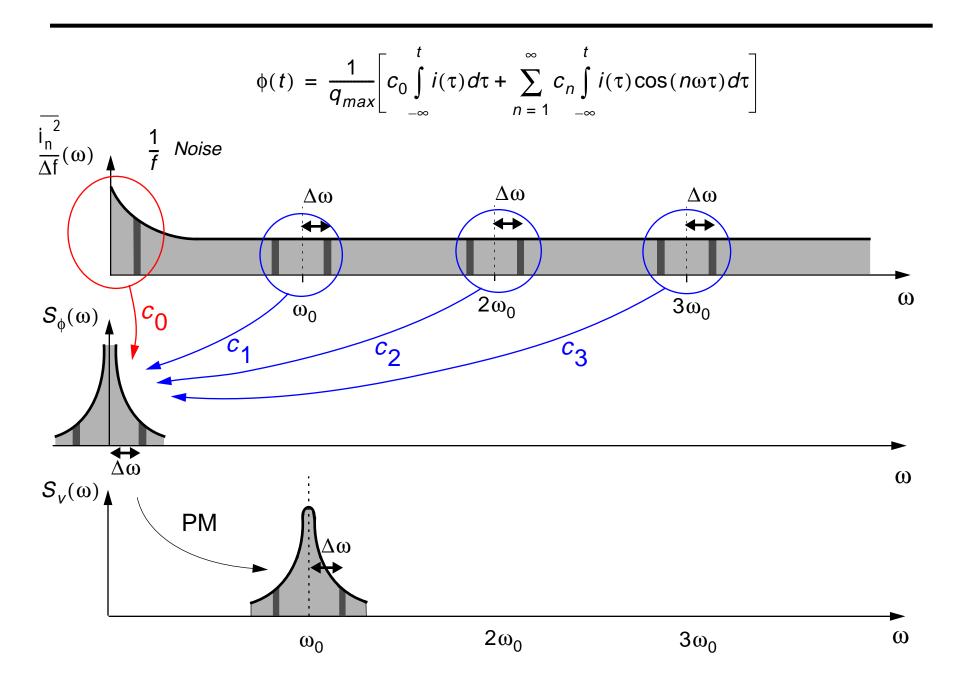

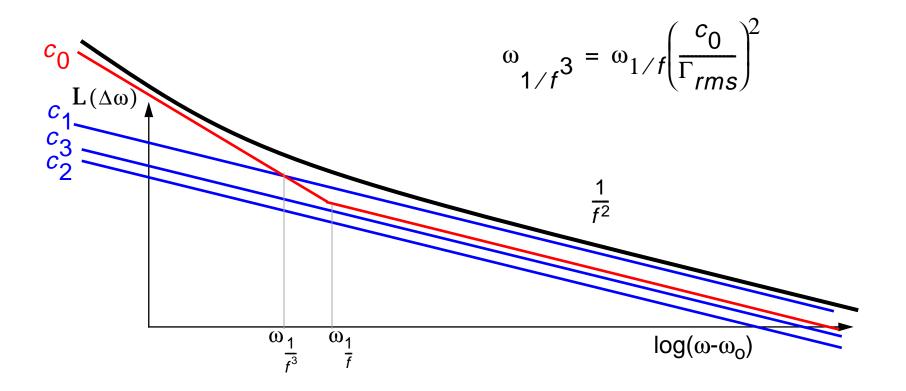

### Noise Contributions from $n\omega_o$

### Effect of Symmetry

The dc value of the ISF is governed by rise and fall time symmetry, and controls the contribution of low frequency noise to the phase noise.

# 1/f<sup>3</sup> Corner of Phase Noise Spectrum

The 1/f<sup>3</sup> corner of phase noise is NOT the same as 1/f corner of device noise

By designing for a symmetric waveform, the performance degradation due to low frequency noise can be minimized.

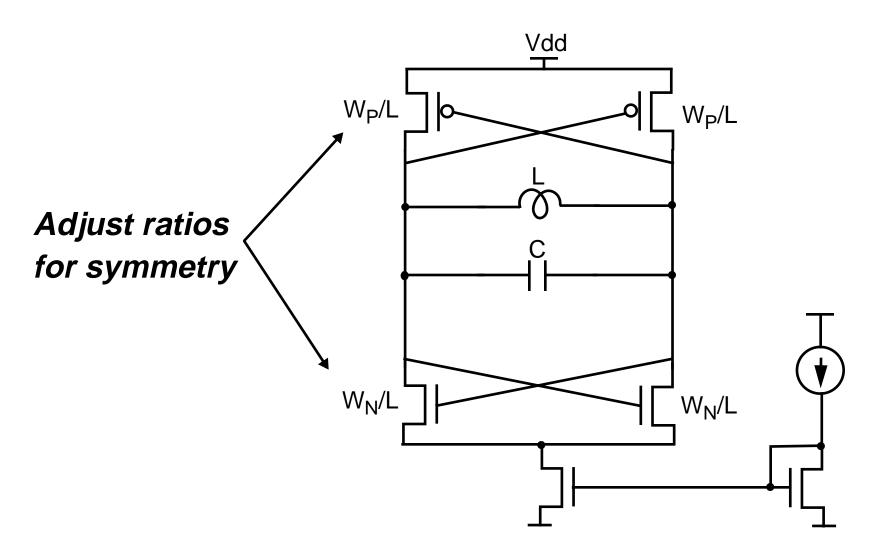

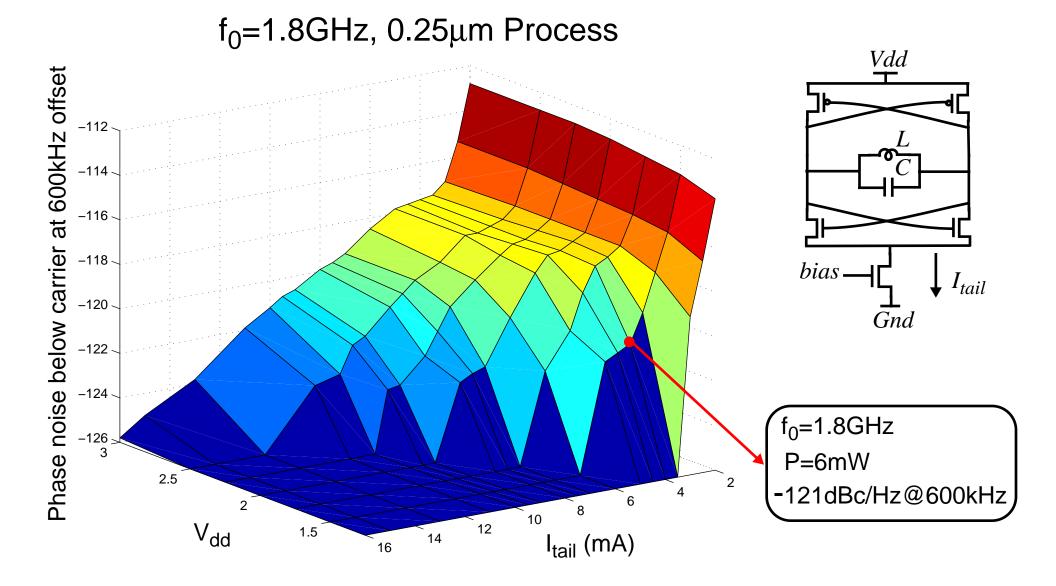

# A Symmetric LC Oscillator

Possible to Adjust Symmetry Properties of the Waveform

# **Complementary Cross-Coupled VCO**

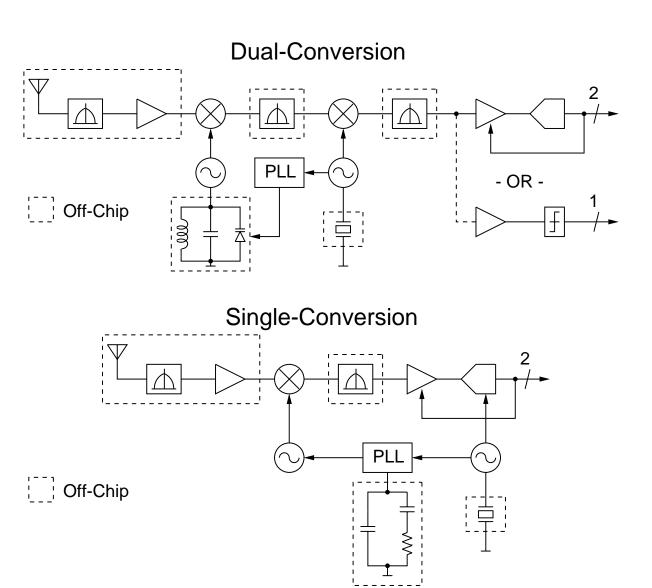

## **GPS OVERVIEW: TYPICAL RECEIVER ARCHITECTURES**

**Distinguishing Features:**

- Typical on-chip  $P_D$  is 100mW 500mW

- Off-chip LNA or active antenna

- Off-chip IF filtering

- 1 or 2 bit quantization

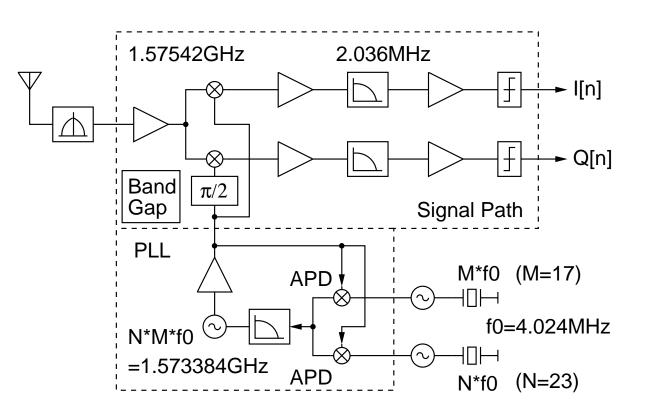

### ARCHITECTURE: LOW-IF RECEIVER

Primary Goal: Make choices to minimize  $P_D$ , maximize integration.

- Low-IF  $\Rightarrow$  On-chip active channel filter.

- Image in GPS band  $\Rightarrow$ Relaxed I/Q matching.

- Eliminate PLL prescaler  $\Rightarrow$  Saves power / noise.

- 1-bit quantization for simplicity.

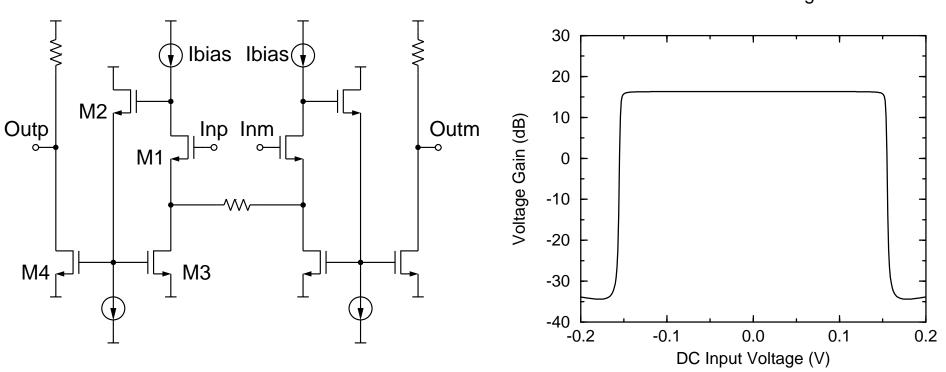

## CIRCUITS: IFA

- Low input capacitance, high linearity.

- Load resistors terminate the active filter input.

Simulated IFA Voltage Gain

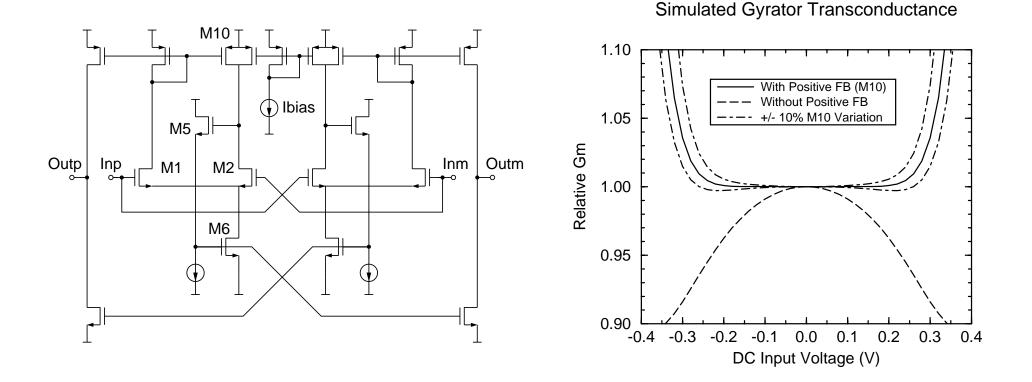

### CIRCUITS: GM-C FILTER (TRANSCONDUCTOR)

Use two *square-law* transconductors to build a *linear*, class-AB transconductor. A little positive feedback (M10) compensates for mobility degradation in M1.

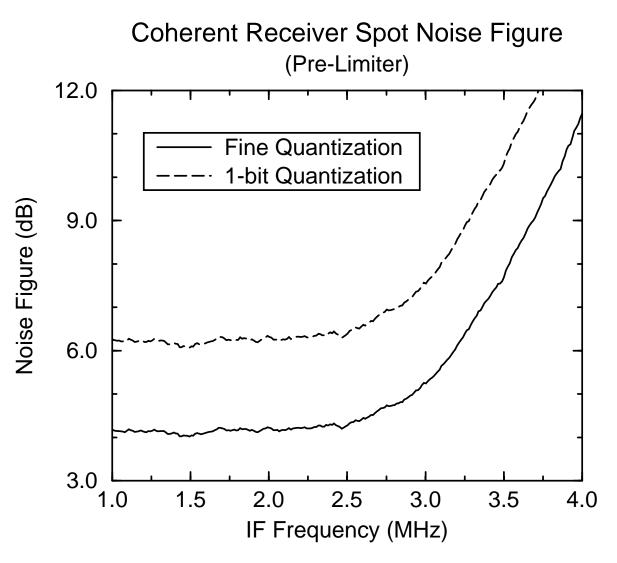

#### EXPERIMENTAL RESULTS: NOISE FIGURE

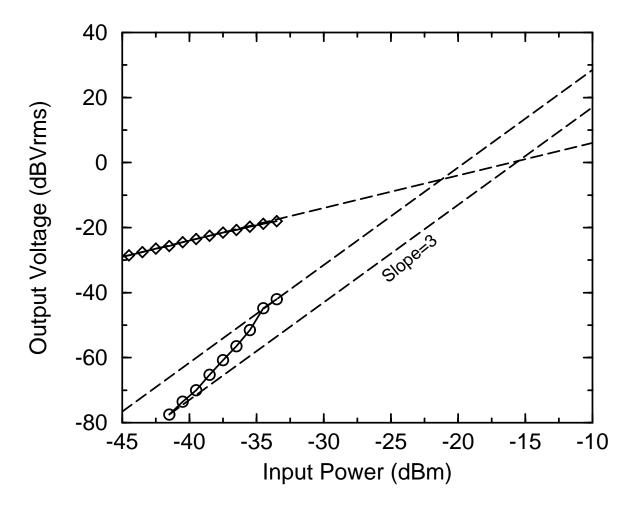

#### EXPERIMENTAL RESULTS: LINEARITY

#### Signal Path 3rd Order Intermodulation

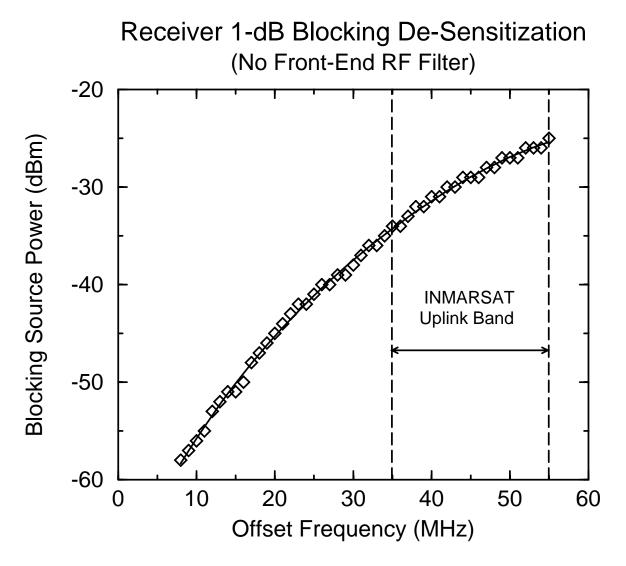

### EXPERIMENTAL RESULTS: BLOCKING PERFORMANCE

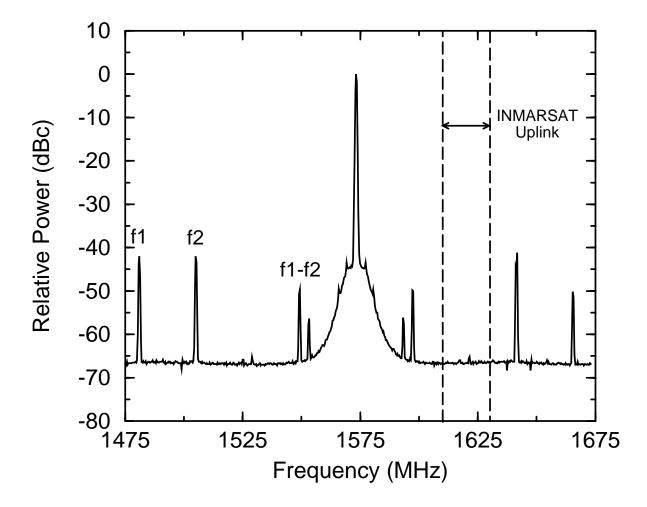

### EXPERIMENTAL RESULTS: PLL SPURIOUS

| Signal Path Performance |                       | PLL Performance   |                      |

|-------------------------|-----------------------|-------------------|----------------------|

| LNA Noise Figure        | 2.4dB                 | Loop Bandwidth    | 5MHz                 |

| LNA S11                 | $\leq$ -15dB          | Spurious Tones    | $\leq$ -42dBc        |

| Coherent Receiver NF    | 4.1dB                 | VCO Tuning Range  | 240MHz ( $\pm$ 7.6%) |

| IIP3 (Filter-limited)   | -16dBm @ -43dBm $P_s$ | VCO Gain Constant | 240MHz/V             |

| Peak SFDR               | 57dB                  | LO Leakage @ LNA  | < -53dBm             |

| Filter Cutoff Freq.     | 3.5MHz                | _                 |                      |

| Filter PB Peaking       | $\leq$ 1dB            | Power/Technology  |                      |

| Filter SB Atten.        | $\geq$ 52dB @ 8MHz    | Signal Path       | 79mW                 |

|                         | $\geq$ 68dB @ 10MHz   | PLL / VCO         | 36mW                 |

| Pre-Filter $G_p$        | 19dB                  | Supply Voltage    | 2.5V                 |

| Pre-Filter $A_v$        | 32dB                  |                   |                      |

| Total $G_p$             | pprox 82dB            | Die Area          | 11.2 $mm^2$          |

| Total $A_v$             | pprox 107dB           | Technology        | 0.5 $\mu$ m CMOS     |

| Non-Coherent Output SNR | 15dB                  |                   |                      |

# **Closing Thoughts**

- CMOS is not ideal, but much more than adequate for many applications.

- □ Scaling trends will continue to improve CMOS.

- □ "RF CMOS" is not an oxymoron anymore.

## Acknowledgments

- Many slides were prepared, and generously supplied, by the following Stanford Ph.D. candidates:

- □ Hirad Samavati (fractal capacitors)

- □ Patrick Yue (spiral inductors)

- □ Ali Hajimiri (oscillator phase noise)

- Derek Shaeffer and Arvin Shahani (LNA work and GPS receiver)